- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Verify MPC5775B/E-EVB Processing/Timing constraints

Verify MPC5775B/E-EVB Processing/Timing constraints

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Verify MPC5775B/E-EVB Processing/Timing constraints

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am researching using this MCU and the specific eval board to control some items.

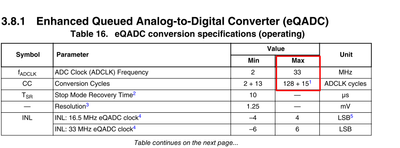

I need to have sub millisecond resolution. I am hoping to connect 64 inputs to the ADC. From looking at the ADC, it can go up to 33 MHz. A conversion cycle takes ~143 cycles, so does that mean to look at all 64 ADC channels, it'll take ~4.29us (33MHz ~30ns. 30ns*132 ~ 4.29us). I don't think I found anything about the mux switching delay?

Does this seem like it should be fine or am I missing something to consider?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes 32 is the channels in one ADC.

And you can convert 2 channels at once. as there are 2 adc modules in one EQADC.

Reading results can be done simultaneously via DMA, So you will read 2 ADCs on conversion complete at once. Much faster then when you use core. But even reading via core will add very small time, but will deplete computing power significantly as you need it to be cyclical reads.

So best way is to use DMA, and free core from any intervention.

So if I wanted to constantly read from all 64 channels, it would be ~275.56 us?

No. that would be time for 128 channels conversion.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Peter! That clarifies a lot!

Just to make sure I'm understanding,

So if I am using the MPC5775E, which has 2 ADCs, it can support up to 128 ADC channels. (although I plan on using the this dev board Link which only has 64 ADC inputs).

since each ADC has 2 ADCs, I can essentially read from 64 ADCs in 1/33MHz * 143 * 32 (32 since each ADC supports 32 channels) = ~139 us.

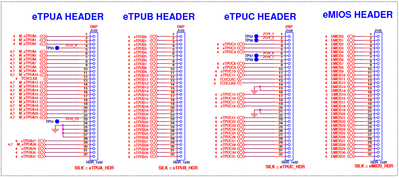

My final concern is the eTPU and eMIOS. This are independent IOs right? So I can independently choose which to go high and which to go low? From looking at the schematic, can you clarify what TP51-52 and TP55-58 correspond to? Why does only eTUPB and eMIOS have the full 32 pin i/o?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

eTPU and eMIOS. This are independent IOs right?

eMIOS is periphery (IP) and eTPU is processing core (its ASIC)

So I can independently choose which to go high and which to go low?

Not sure about this, but if you are talking about signal levels, then yes.

Why does only eTUPB and eMIOS have the full 32 pin i/o?

If you are asking about board implementation, then it is because the design decided that way.

can you clarify what TP51-52 and TP55-58 correspond to?

TP = test point. Not sure what document you are referring to.

Check out MPC5775BE EVB User Guide for details.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

eMIOS is periphery (IP) and eTPU is processing core (its ASIC)

Not sure about this, but if you are talking about signal levels, then yes.

So functionally, they're essentially the same with the application being I/O (except one is NXP proprietary while the other is just fast I/O since it has its own processor per eTPU site)? My application is that I just need to be high or low based upon user decisions.

TP = test point. Not sure what document you are referring to.

Check out MPC5775BE EVB User Guide for details.

The document I am referring to is the eval board schematic (the image that I previously attached). I was hoping to check the user guide, but it appears there isn't one for this specific board and only the other board you mentioned. Board I was hoping to find the user guide. There's a quick start guide but that appears mostly software programming and a quick overview of the boards functionality.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

So functionally, they're essentially the same with the application being I/O (except one is NXP proprietary while the other is just fast I/O since it has its own processor per eTPU site)? My application is that I just need to be high or low based upon user decisions.

Well, if you look at it as black box outputting signal level high or low. then yes.

The document I am referring to is the eval board schematic (the image that I previously attached). I was hoping to check the user guide, but it appears there isn't one for this specific board and only the other board you mentioned. Board I was hoping to find the user guide. There's a quick start guide but that appears mostly software programming and a quick overview of the boards functionality.

Have a look at following link:, there is user guide.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Your calculation seem to me not precise:

If I take max from datasheet:

(1/33Mhz ) * 143 * 32 = 138,6us

As you want to convert 64 channels and have 2 ADC units.

I don't think I found anything about the mux switching delay?

There is no delay defined. So I guess i fragment of a clock.

Best regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is the 32 from the 32 channels in each ADC?

So if I wanted to constantly read from all 64 channels, it would be ~275.56 us?

Could you clarify what you mean a fragment of a clock? Like give or take a couple clock cycles (so a handful of ns per read)?