- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- PCA21125 SPI problem

PCA21125 SPI problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PCA21125 SPI problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi :

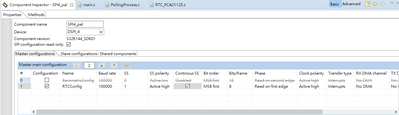

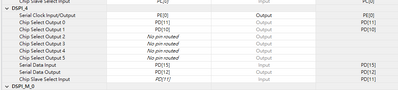

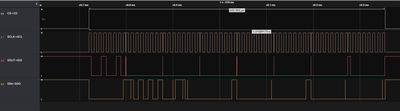

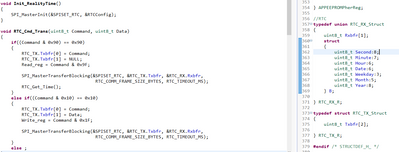

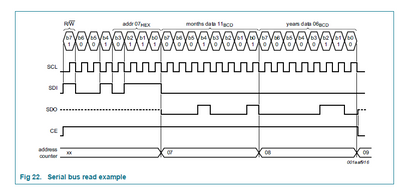

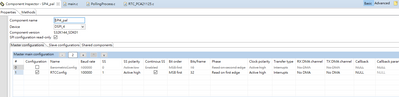

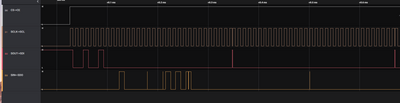

I'm using PCA21125 with SPI to do RTC function on 5746R. Here's my SDK setting(fig1/2, CS out1 in DSPI4). When I set command in "RTC_Cmd_Trans(0x92, 0)" to read time data from second(I haven't used "SPI_SetSS" to set CS1_4 = high). The initial SPI4 sout from MCU always be high, but it should be low which showd in PCA21125 spec.

How should I fix it? Or is there any sample code? thanks.

BR,

Xantia

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I understand initial level on SDO does not matter for this config and RTC device. With (CPOL=0, CPHA=0) config, once CS is asserted the SPI is placing first data bit on SOUT. After defined delay (tCSC, PCS to SCK delay) the master outputs the first edge of SCK and the master and slave devices use this edge to sample the first input data bit on their serial data input signals. At second SCK edge output data are changed. You should rather config SCK to PCS delay, PCS to SCK delay and delay between transfers for some reasonable values. DSPI_MasterSetDelay function can be used.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi :

So how should I set SDK to make sout of SPI4 to be initail low? Cause I try lots of associations, just can't make it(fig2).

BR, Xantia

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

if Fig22 shows SDI low before CS asserting, it does not mean it must be low. For device it is don't care, it is deselected For used SPI mode asserting CS both master and slave shift first bit on its output. So signals should be fine, just you should play little bit with delays, as I wrote.

BR, Petr