- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5777C: FCCU->RCCU_0 Error

MPC5777C: FCCU->RCCU_0 Error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

I am working with MPC5777C processor and i am getting a RCCU_0 error. (Safety cores out of sync during lockstep).

Checker Core is enabled (I verified this by reading the SIU_Lockstep Register and bit 42 in FCCU Register)

I cannot find any documentation to know why the RCCU_0 error might be occuring.

Has anyone else had this issue? Could you Point me tp any available documentation.

Thanks,

Amey

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is most probably caused by your software.

I expect incorrect core register initialization. Make sure you initialize all core registers by 64-bit.

I have tried it on few fresh samples without code and no RCCU error occurred.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1. What is the impact of wait instruction that will impact setting RCCUx error ?

Having wait instruction is triggering RCCU error.

2. Can't we use wait instruction, if we have to use wait, what we need to do to get rid of RCCU error

-Joshua

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the tip. I shall try it out.

Do you know what does RCCU_0 bit indicate? Is there any Information in any document on the subject?

Thanks,

Amey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is most probably caused by your software.

I expect incorrect core register initialization. Make sure you initialize all core registers by 64-bit.

I have tried it on few fresh samples without code and no RCCU error occurred.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

We are using MPC5777C processor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You still see RCCU_1 error?

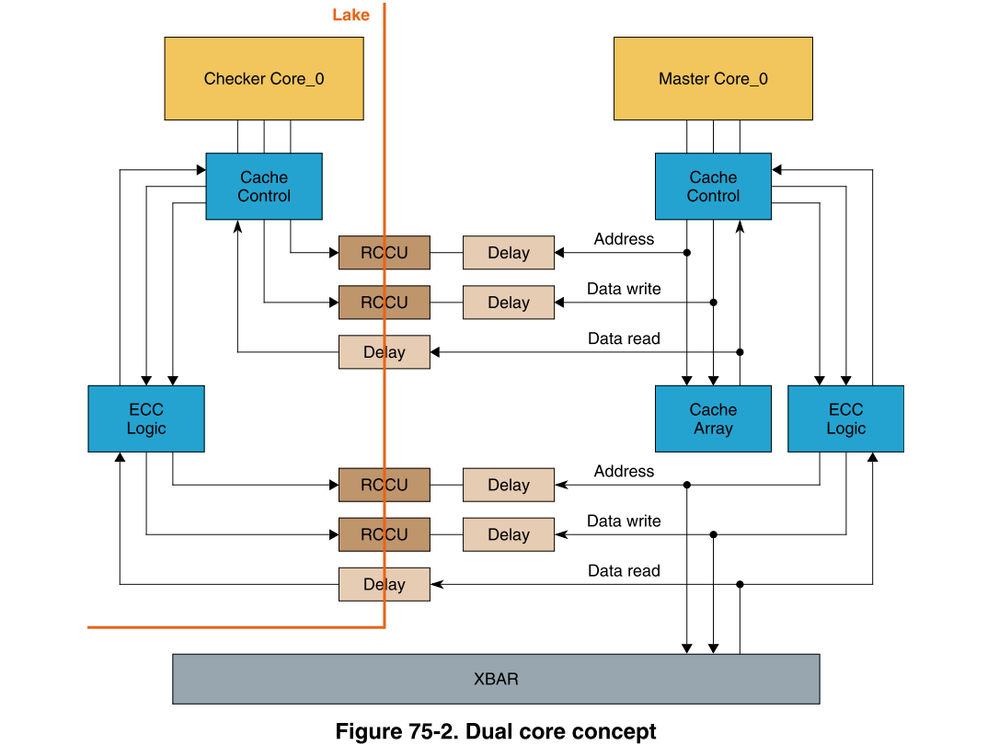

RCCU_0 Means a mismatch inside the z759 core. RCCU_1 is a mismatch at the bus gasket interface between the core and the system bus. So basically a read or write access didn't match from both cores. In both cases, it means the core and it checker are "out of sync". There's no recovery mechanism for this so the reaction needs to be reset and restart in both cases.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

Can you send me the list of core registers that needs to be initialized. To my knowledge, we have initialized all the registers, still we end up in RCCU error.

Please help

-Joshua

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In case of someone else having the same problem:

I have initialized the following registers to prevent RCCU0 error:

Core Registers r0...r31 (with evsplatfi)

TBL, TBU (spr 284, 285) (with mtspr)

USPRG0 (spr 256)

CTR (spr 9)

LR (spr 8)

SPRG 0-9 (spr 272...279, 604, 605)

SRR 0-1 (spr 26, 27)

CSRR 0-1 (spr 58, 59)

DSRR 0-1 (spr 574, 575)

MCSSR 0-1 (spr 570, 571)

IVPR (spr 63)

DEAR (spr 61)

MCAR (spr 573)

DEC, DECAR (spr 22, 54)

Tobias

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello guys,

At the moment, I'm facing the same problem. Could you send me the assembly instructions you have written?

Best regards,

Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello guys,

At the moment, I'm facing the same problem. Could you send me the assembly instructions you have written?

Best regards,

Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Tobias, will test and update

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

we have solved the RCCU_0 error by initializing the core registers that have an unaffected value after startup.

Now there is still a permanent error of RCCU_1. What does cause this error? Have I still forgot some registers?

Tobias