- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC574x CANFD @4MBPS

MPC574x CANFD @4MBPS

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC574x CANFD @4MBPS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have been trying to test the CANFD with different speeds. currently I am able to work the CANFD at 2 MBPS. The register initialization is as follows.

the Baudrate resgisters are configured to 500 kbps and Data rate registers are configured with 2 MBPS. The fcanclk is 40Mhz.

lp_FlexCan_fd->CTRL1.B.PRESDIV = 0x03;

lp_FlexCan_fd->CTRL1.B.PROPSEG = 0x07;

lp_FlexCan_fd->CTRL1.B.PSEG1 = 0x05;

lp_FlexCan_fd->CTRL1.B.PSEG2 = 0x04;

lp_FlexCan_fd->CTRL1.B.RJW = 0x02;

lp_FlexCan_fd->FDCBT.B.FPRESDIV = 0x01 ;

lp_FlexCan_fd->FDCBT.B.FPROPSEG = 0x03 ;

lp_FlexCan_fd->FDCBT.B.FPSEG1 = 0x02 ;

lp_FlexCan_fd->FDCBT.B.FPSEG2 = 0x02 ;

lp_FlexCan_fd->FDCBT.B.FRJW = 0x02 ;

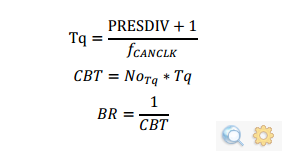

I want to test the CANFD with 4 MBPS so ... I did the calculations using this algorithms by keeping PRESDIV to 0 and I got the N0Tq as 10. And I kept the initialzation as below

lp_FlexCan_fd->CTRL1.B.PRESDIV = 0x03;

lp_FlexCan_fd->CTRL1.B.PROPSEG = 0x07;

lp_FlexCan_fd->CTRL1.B.PSEG1 = 0x05;

lp_FlexCan_fd->CTRL1.B.PSEG2 = 0x04;

lp_FlexCan_fd->CTRL1.B.RJW = 0x02;

lp_FlexCan_fd->FDCBT.B.FPRESDIV = 0x00;

lp_FlexCan_fd->FDCBT.B.FPROPSEG = 0x03;

lp_FlexCan_fd->FDCBT.B.FPSEG1 = 0x02;

lp_FlexCan_fd->FDCBT.B.FPSEG2 = 0x02;

lp_FlexCan_fd->FDCBT.B.FRJW = 0x02;

But this configuration is not working for me.. So please have look into my intialization and correct me if I am doing anything wrong in here

And I would be nice if you can clarify me how the PROPSEG, PSEG1,PSEG2 is calculated once we get the N0Tq = 10,12..... etc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Petr,

That really was helpful. Thanks for that assistance.

I have a further question. How to configure the data rate to 3Mbps..

I tried calculating this formulas.. But its not working for me..

I would really appreciate if you can help me on this. to initlaize my Data rate registers.

regards

Akshay H V

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Akshay,

from the formulas, you gave, you can get

(PRESDIV+1) * NoTq = fCANCLK / BR

Then assuming PRESDIV and NoTq are integer values only, there is no possible setting for given PE clock and baudrate.

Different PE clock has to be used.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Petr,

Just for my understanding you are mentioning that the fcanclk has to be

changes from current 40Mhz.. to something else.. to achieve the 3 MBPS

data rate..??

Regards

Akshay H V

SWP FBL developer

Interior-Body and Security

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you are right.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have Transceiver Delay Compensation enabled (FDCTRL[TDCEN]=1)?

If not (FDCTRL[TDCEN]=0) then the transceiver loop delay time could be longer than the actual sample point delay (200ns with your setting). The FlexCAN then detect a bit error in data phase.

That’s why the Secondary Sample Point is defined and used when TDC is enabled.

If TDC is used, what is FDCTRL[TDCOFF] setting in fact? What is read from FDCTRL[TDCVAL]?

Theoretically the TDCOFF should be set to the middle of the data bit time, so

TDCOFF = bit_time/2 * PEclock = 250ns/2 * 40MHz = 5.

BR, Petr