- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

オプション

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

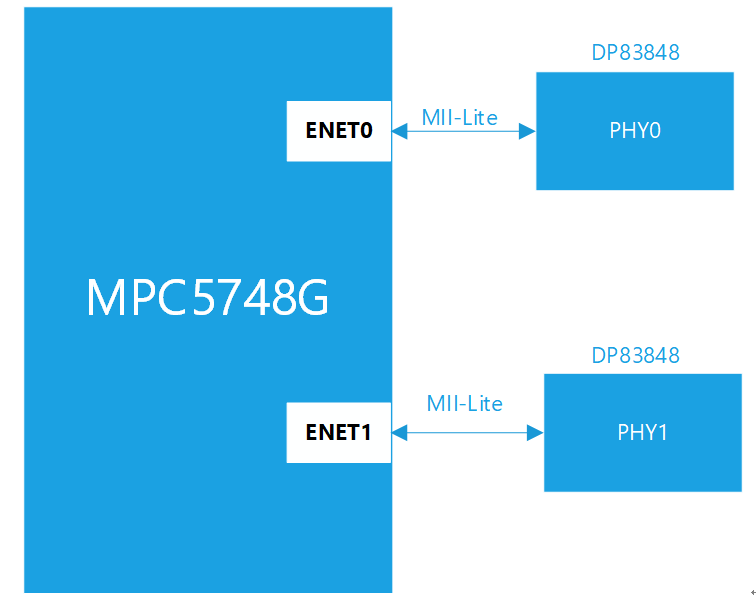

MPC5748G MII-LITE Dual Ethernet Communication (ENET0 ENET1 working simultaneously)

05-16-2018

01:44 AM

1,699件の閲覧回数

liuweiliang

Contributor II

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Problem description : PHY0 chip corresponding to the ENET0 resource is transmitting normally and the receiver can enter the interrupt but the received data is incorrect.The transmission and reception of the PHY1 chip corresponding to the ENET1 resource is abnormal. Code Reference AN4830 Qorivva Recipes for MPC574xG Code Sample Code for Ethernet Folder。

Hardware:

The MII-Lite interface is defined as follows;

| MPC5748G | PHY0 | MPC5748G | PHY1 | ||

No. | MODULE | pin | pin | MODULE | pin | pin |

1 | ENET0 | PG13 | TXD3 | ENET1 | PI13 | TXD3 |

2 | PG12 | TXD2 | PH3 | TXD2 | ||

3 | PH0 | TXD1 | PA10 | TXD1 | ||

4 | PH1 | TXD0 | PA11 | TXD0 | ||

5 | PH2 | TXEN | PI12 | TXEN | ||

6 | PG1 | TXCLK | PE12 | TXCLK | ||

7 | PE13 | RXD3 | PB6 | RXD3 | ||

8 | PA7 | RXD2 | PB7 | RXD2 | ||

9 | PA8 | RXD1 | PD9 | RXD1 | ||

10 | PA9 | RXD0 | PD10 | RXD0 | ||

11 | PF15 | RXDV | PB5 | RXDV | ||

12 | PA3 | RXCLK | PB11 | RXCLK | ||

13 | PG0 | MDC | PG0 | MDC | ||

14 | PF14 | MDIO | PF14 | MDIO | ||

CODE:

1 返信

07-15-2021

04:42 AM

1,142件の閲覧回数

d_bi

Contributor I

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你好,请问问题解决了吗?我现在跟你遇到了同样的问题,能否跟你交流学习下?