- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5744P - SPI change clock polarity between chip selects (CTAR)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm interested in connecting two devices to the same SPI bus which differ on the idle clock polarity (defined as CPOL).

The MPC5744P i'm working on provides a clever resource to deal with this, which are the CTAR registers and the CTAS field when performing a TX write.

However, I have a question I've been unable to answer reading through the documentation.

If transfer #0 is made to CS0 with CPOL=0 (using CTAR0 config), and then transfer #1 is made to CS1 with CPOL=1 (using CTAR1 config):

a) Clock polarization change happens before CS assert (ideal)

b) Clock polarization change happens after CS assert (unfeasible, as the clock change may count as a valid shift)

Please provide me with evidence on documentation of either answer, as this will condition my entire design.

Best regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

option no.A is correct unless SPI is configured for Continuous Selection Format is selected, in this case polarity change is not allowed.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

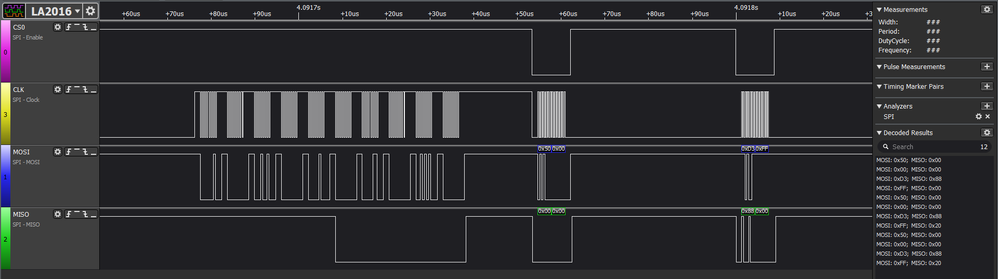

Hi, I have the same application that two devices connect to one SPI bus with different clk polarity. And I have measured the waveform when two devices communication, as shown below (CS1 is not measured).

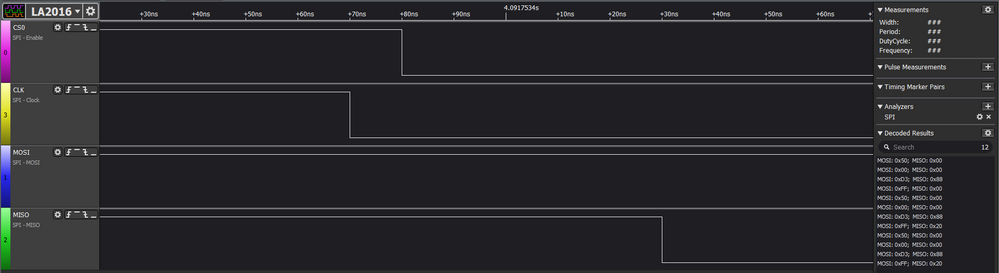

I found that CLK will change before CS assert. But the timing does not meet the requirements. Time betwwen CLK change and CS assert is only 10ns, the deviece connect to CS0 require 75ns. This will cause the communication failure. The enlarged waveform is as shown below.

Is there some way to configure the delay after CLK changed?