- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

MPC5643L_FlexPWM_question(reload and interrupt)

Aboout FlexPWM

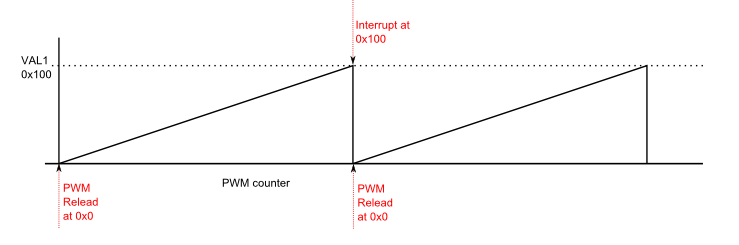

Q1: If the VAL1 is required for register reloading and an interrupt, which will happen first, reloading or interrupt?

For example:

FLEXPWM_0.SUB[0].CTRL.B.FULL = 1; // Full cycle reload

FLEXPWM_0.SUB[0].VAL[1].R = 600; //FLEXPWM0_VAL1; // Max value for counter

FLEXPWM_0.SUB[0].TCTRL.R = 0x1; //Enable CTU trig only for VAL1

CTU.TGSISR.R = 0x00000800; // active input = PWM_EVEN0 (VAL1 - VAL3 - VAL5 OUT_TRIG1_0 )

CTU.TGSCR.R = 0x0000; //triggered mode

//Compare modulo & reload value

CTU.T0CR.R = 0;

CTU.TGSCRR.R = 0;

CTU.TGSCCR.R = 1200;

//Trigger Handler control registers

CTU.THCR1.R = 0x00000040; //T0: enable

CTU.THCR2.R = 0x00000000; //T4-T7: disable

//Interrupt enable

CTU.CTUIR.R = 0x0100;//T0 interrupt enable

void PWM0_sub0__CTU_T0_Isr(void)

{

...

FLEXPWM_0.SUB[0].VAL[2].R =x;

}

If in the k cycle , the value we read FLEXPWM_0.SUB[0].VAL[2] is 100 and the value currently using

( FLEXPWM_0.SUB[0].VAL[2]) is 200 ,

Case 1: in the k+1 cycle , the value we read FLEXPWM_0.SUB[0].VAL[2] is x and the value currently using( FLEXPWM_0.SUB[0].VAL[2]) is 100;(reload first,interrupt second)

Case 2: in the k+1 cycle , the value we read FLEXPWM_0.SUB[0].VAL[2] is x and the value currently using( FLEXPWM_0.SUB[0].VAL[2]) is x; (interrupt first, reload second)

Which case is right?

Thanks very much!

Yanna

Hi,Peter.petervlna

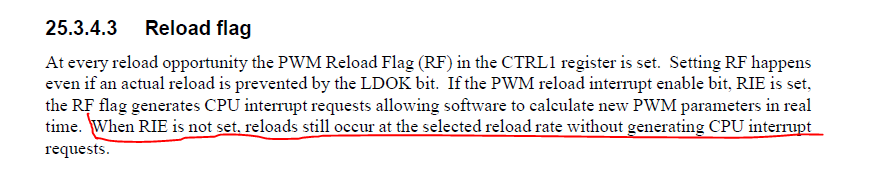

I think that reload and reload interrupt are different. The loading of the INTI and VALx registers will occur even if the reolad interrupt is disable. Is it right?

I think my question is about reload and trigger interrupt, but your reply talks about reload interrupt and trigger interrupt, Is it right?

P685 (MPC5643L reference mannual) ,there exits a sentence:

Thanks very much!

Yanna

- About PWM petervlna

Q3:

(1) If I set the value of the Mask Register 0x0330(PWMA and PWMB output of the submodule 0 and 1 are forced to logic 0), at the same time CTRL2.B.INDEP=0(complentary PWM pair, the submodule 0 and 1) when a force out signal occur, will the PWMA and PWMB be the logic 0?

(2) If OUT23_0=0 and OUT45_0=0(SEL23_0=10, SEL45_0=10, OUT23_0 and OUT45_0 bit is used by the deadtime logic), at the same time CTRL2.B.INDEP=0(complentary PWM pair, the submodule 0) when a force out signal occur, will both the PWMA and PWMB (the submodule 0) be the logic 0 or will an error occur ?

Thanks very much!

Yanna

Hi,Peter. I have another question about the code above.

- About CTU

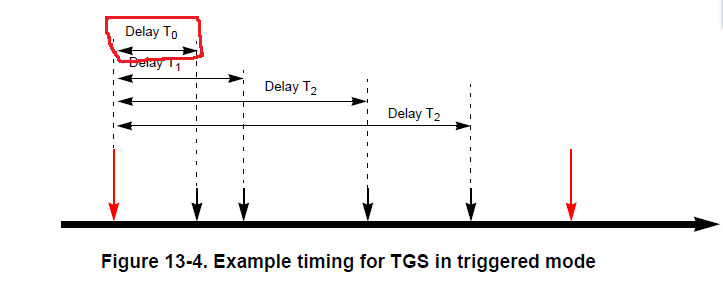

Q2: can I set the value of CTU.T0CR(Trigger 0 compare value) same as the CTU.TGSCRR(TGS counter reload value) ? If both

are equal, will trigger 0 occur? like

CTU.T0CR.R = 0;

CTU.TGSCRR.R = 0;

Addition:(That says I want when the count value equal the VAL1 value, trigger 0 (TGS) occur at the same time,

the ADC command also occur at the same time, delay T0=0 . )

Thanks very much!

Yanna

Hi,

I did some testing to verify the behavior.

If reload and VAL1 interrupt are set for same timing, first time after enabling of FlexPWM module only reload interrupt will come.

In second and every following period the VAL1 interrupt and reload interrupt are triggered at the same time as the compare is done via hardware. Both interrupt requests are send to INTC module at the same time.

If in INTC the priority for VAL1 and reload interrupts are same then reload interrupt is served first (as its number in interrupt table is lower) and then VAL1 interrupt is served.

If you set priority for those interrupts then interrupt with higher priority is called first.

Peter