- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

GPIO access for MPC5746R

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have been reading through the MPC5746R reference manual but I couldn't get the following information.

Assuming two cores (core-0 and core-1+2 in LS) running in decoupled parallel mode,

How are the peripherals mapped to the two cores? If there is data on one of the IO pins, can both the cores access this data simultaneously? Or are the peripheral pins configured to one core??

Rephrasing the question -> How does the peripheral access work (SIUL2) for the MPC5746R ??

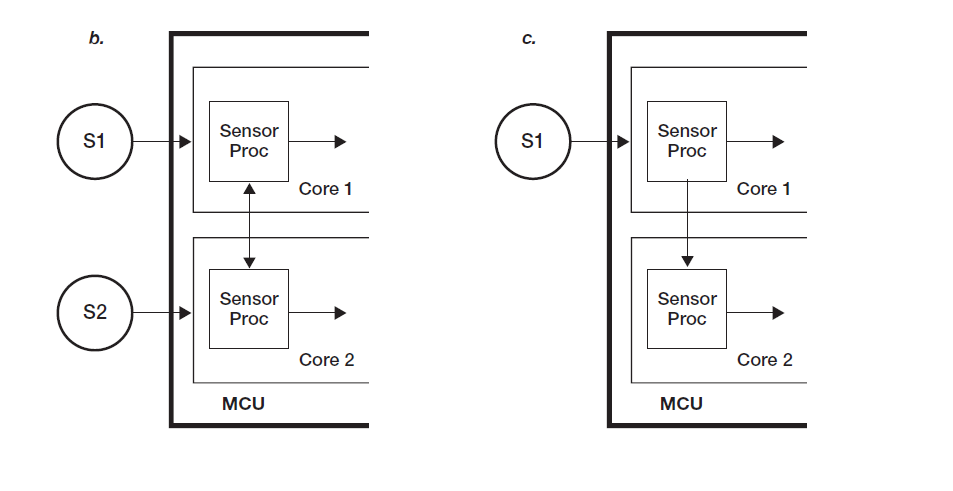

Intention: From safety perspective I would like to understand how sensors are accessed from the two cores.

Thank you :smileyhappy:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, it is interesting question.

I know the picture, it is taken from some document related to MPC5643L device, having two cores, where it is possible to choose between two operating modes (LSM or DPM).

However in case MPC5746R, you have two cores in lockstep (Main Core_0 and Checker Core_0s) where it is expected to run safety software and another core (Main Core_1) where it is assumed to run non-safety software.

No DPM mode exists.

Regarding peripherals (but also internal memories). You can access by any core to any internal resources (exluding local core registers) where prioritizing is given XBAR:

What is the advantage of Crossbar Switch

SIUL2 registers are accessed over Peripheral Cluster A by both cores -

In case Main Core 0, it goes over M0/M1 of Computational shell XBAR to Peripheral shell XBAR over Bridge (S7-M3)

and then to AIPS PBridge_0 (S7).

In case Main Core 1, it goes over M2/M3 of Computational shell XBAR to Peripheral shell XBAR over Bridge (S7-M3)

and then to AIPS PBridge_0 (S7).

Accesses are prioritized according XBARs setting.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

(Ignoring checker_core_0s for now) Rephrasing the information you have provided with a similar question :smileyhappy:

1. Main core0 and Main core1 do NOT run in parallel mode? If they're independent of each other, they can anyways be run in parallel mode right??? (My understanding of a decoupled parallel mode is that the two cores are independent of each other and can be run in parallel. Please correct my understanding if I am wrong or am missing more info).

2. Peripherals are tied to cluster A whose information is then available on the XBAR for the two cores to read. This I understand from the block diagram of MPC5746R. I also understand from the link you shared that the two cores (can be seen as masters) can simultaneously "connect" to the peripherals through the XBAR. But does that mean I can simultaneously read the same registers from the two cores?? Taking an example --> ADC channel 0 has converted some analog data (maybe from a pressure sensor) to digital data. This is available in the buffer registers. Now can I access this data from Core0 AND Core1 (I want the exact SAME data on both the cores). If yes, how can I do this??

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1) It it just about terminology. Decoupled Parallel Mode (DPM) means that disabling of lockstep mode frees the checker core for independent execution how it is possible on MPC5643L device. But OK, Main Core_0 and Main Core_1 are just independent.

2) No, it cannot be read simultanously because the access goes over same port AIPS PBridge_0 (slave S3 of XBAR1). An access will be prioritized according setting of XBAR1_PRS3 and XBAR1_CRS3 registers. If you need to read the same register by two cores, then this reads will be in sequence.