- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- FMPLL configuration for MPC5644A

FMPLL configuration for MPC5644A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FMPLL configuration for MPC5644A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

pls help anyone how to configure fmpll in mpc5644a by Fref =40 MHZ for Fsys=120MHZ

i configured but it not working in EVT board ..my configuration is

void FMPLL_config()

{

ECSM.MUDCR.R = 0x40000000; /* 1 SRAM waitstate for fsys above 98MHz */

FMPLL.ESYNCR2.R = 0x00000002;

FMPLL.ESYNCR1.R = 0xF0020024;

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */

FMPLL.ESYNCR2.R = 0x00000001; /* Fsys =120Mhz */

SIU.ECCR.R = 0x00001003; /* CLKOUT to /4 because of 66MHz limit */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David Tosenovjan,

Thanks..i solved it..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David Tosenovjan,

Thanks for your reply..i looked my board is XPC564AKIT324S uses 40MHz crystal.still it is not working..if there any jumper settings in that board for working Fmpll?

Thanks & Regards,

chandrasekar k

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

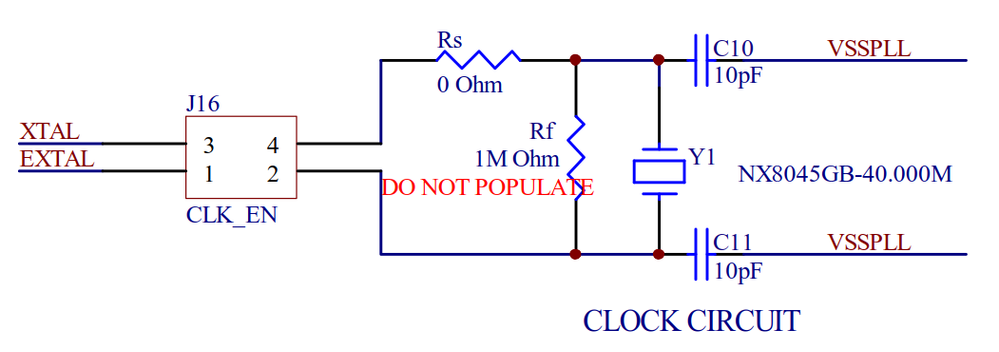

Check jumpers J16 whether there aren't removed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin Kovar,

I tested your code in XPC564A 324BGA MINIMODULE BOARD(MPC5644A), but board is not responding..do you have any suggestions for this..

any jumper settings in this board or anything..

Regards,

Chandrasekar K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please, pay attention to following example code, function FMPLL_init:

https://community.freescale.com/docs/DOC-101455

Code selects used board at the beginning of main function by following macros:

#define XPC564AKIT176S 0

#define XPC564AKIT208S 1

#define XPC564AKIT324S 2

/* Choose one of 3 options above according to your configuration */

#define USED_BOARD XPC564AKIT324S

Possible issues are:

- XPC564AKIT176S and XPC564AKIT208S use 8MHz crystal

- XPC564AKIT324S uses 40MHz crystal

- 1 SRAM waitstate for fsys above 98MHz

- CLKOUT frequency must be 66MHz at most

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

try this configuration:

/* Set sysclk = 120MHz running from PLL with 40 MHz crystal reference. */

void initSysclk (void) {

FMPLL.ESYNCR1.B.CLKCFG = 0X7; /* Change clk to PLL normal mode from crystal */

FMPLL.SYNCR.R = 0x22880000; /* Fsys =60Mhz */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK */

FMPLL.SYNCR.R = 0x22800000; /* Fsys =120Mhz */

}

Regards,

Martin