- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- ECSM - Some Questions

ECSM - Some Questions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ECSM - Some Questions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I have multiple questions that I met when I read the MPC5674FRM, Application Note AN5200 and Application Note AN4513.

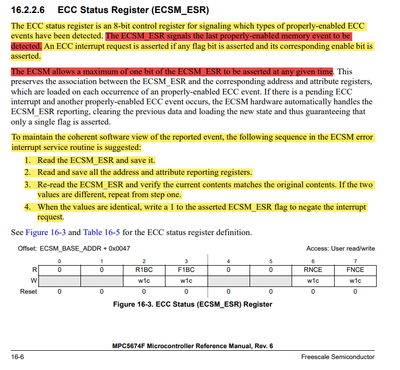

1 - In ECSM_ESR register part of RM, why re-reading the ECSM _ESR suggested? Is it just to be sure we read the ECSM_ESR correctly? The related figures is below;

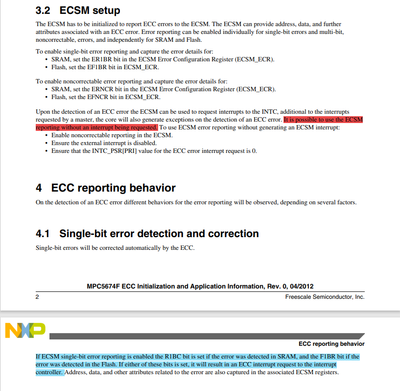

2 - In 3.2 ECSM part of AN4513, there is information about using ECSM reporting without an interrupt is requested. I understand from this information, we can just use ECSM reporting without interrupts. (I don't want to handle the errors, I just want to know there is a problem.)

However, in 4.1 Single-bit error detection and correction Section of AN4513, I understand that if we set the R1BC and F1BR, it will result in an ECC request to the interrupt controller.

So I think there is a discrepancy. Can you give me a hand to figure out the topic?

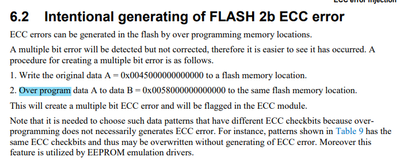

3 - What is the meaning of "over program" which is seen in AN5200? How does writing the data B to the same flash memory location creates multiple bit ECC error?

Best regards,

Mert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) It is just prescribed sequence that is needed to keep in order to have valid results. In the code it seems as follows:

for (;;)

{

/* 1. Read the ECSM_ESR and save it */

ecsm_esr = (uint8_t)ECSM.ESR.R;

/* 2. Read and save all the address and attribute reporting registers */

ecsm_rear = (uint32_t)ECSM.REAR.R;

ecsm_remr = (uint8_t)ECSM.REMR.R;

ecsm_reat = (uint8_t)ECSM.REAT.R;

/* 3. Re-read the ECSM_ESR and verify the current contents matches

the original contents. If the two values are different, go back

to step 1 and repeat */

if (ecsm_esr == (uint8_t)ECSM.ESR.R)

{

break;

}

}

/* 4. When the values are identical, write a 1 to the asserted ECSM_ESR flag

to negate the interrupt request - we actually negate both flags */

ECSM.ESR.R = 0x03;

2) ECSM interrupts may not be used. But reading 2-bit affected data always reads in bus error i.e. machine check exception. This exception cannot be disabled.

3) It means program without erase in between. In the flash it creates data pattern affected by ECC error.