- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx Knowledge Base

- :

- Example MPC5744P SWT Short reset GHS614

Example MPC5744P SWT Short reset GHS614

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Example MPC5744P SWT Short reset GHS614

Example MPC5744P SWT Short reset GHS614

********************************************************************************

* Version: 1.0

* Date: Oct-22-2014

* Classification: General Business Information

* Brief: This example demonstrate SWT functionality

* On SWT timeout it sent signal to FCCU where is short

* functional reset reaction on SWT timeout configured

* FCCU then sent signal to RGM module which triggers short

* functional reset.

********************************************************************************

* Test HW: MPC57xx

* Maskset: 1N65H

* Target : internal_FLASH

* Fsys: 200 MHz PLL with 40 MHz crystal reference

********************************************************************************

Revision History:

1.0 Oct-22-2014 b21190(Vlna Peter) Initial Version

1.1 Mar-24-2015 b21190(Vlna Peter) Added SWT short reset

*******************************************************************************/

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello Peter,

we experienced some problems when using your sources in S32 design studio (Power, v1.1).

We are working on a NXP Evaluation Board MPC5744P 257BGA, Flash tool is Multilink Universal.

You have uploaded two similar projects (both GHS) called long reset and short reset. We used short reset and copied the code into a

brand new S32ds Project for Panther MPC5744P. Please see below for the main.c and some remarks on the Startup.S.

What happened ? First of all we got stuck in FCCU_Init(), because the operation was always aborted:

void FCCU_Init(void)

{

/* Unlock configuration */

FCCU.TRANS_LOCK.B.TRANSKEY = 0xBC;

/* provide Config state key */

FCCU.CTRLK.R = 0x913756AF;

/* enter config state - OP1 */

FCCU.CTRL.R = 0x1;

/* Verify if state change was sucessful */

while (FCCU.CTRL.B.OPS != 0x3); //operation status successful

Then we called your function FCCU_clear_faults() not only in the main (why do you call it there??), but before the FCCU_Init(). And then operations were successful.

Actual Problem:

But now when running you application in S32ds there are no resets at all. I wonder whether the Startup.S and SWT_Init() might be the problem ?

I observed in your projects "long" and "short" that SWT_Init() is not the same in both projects.

Can you probably help me get the S32ds project running ? I will send you any files upon request.

Thanks + best regards

Lars

PS:

I'd like to send you the sources but I cannot upload a zipped folder. So here is the main.c which should also be sufficient, I guess.

Please also look at your startup.S (auto generated in s32ds) which says:

;#****************************** Turn off SWT ********************************

;#SWT0

e_lis r4, 0xFC05

e_or2i r4, 0x0000

e_li r3, 0xC520

e_stw r3, 0x10(r4)

e_li r3, 0xD928

e_stw r3, 0x10(r4)

e_lis r3, 0x7F00

e_or2i r3, 0x010A

e_stw r3, 0(r4)

--> shouldn't there be 0xFF00 and 0x010B ?

******************************************

main.c

/*

* main implementation: use this 'C' sample to create your own application

*

*/

#include "derivative.h" /* include peripheral declarations */

#define DRUN_MODE 3

extern void xcptn_xmpl(void);

/*******************************************************************************

* Local functions

*******************************************************************************/

/*******************************************************************************

Function Name : Sys_Init

Engineer : b21190

Date : Oct-22-2014

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : Clock settings

Issues : NONE

*******************************************************************************/

void Sys_Init(void)

{

//Clk Out

MC_CGM.AC6_SC.R = 0x02000000; //Enable PLL0 - clkout0 //MC_CGM_AC6_SC

MC_CGM.AC6_DC0.B.DE = 1; //Enable divider for SYSCLK0

MC_CGM.AC6_DC0.B.DIV = 3; //Set divider for SYSCLK0 (div by 4)

//Configure RunPeripheralConfiguration regist ers in ME_RUN_PC0

MC_ME.RUN_PC[0].B.DRUN = 1; //Enable DRUN mode for all peripherals using ME_RUN_PC[0]

MC_ME.DRUN_MC.B.XOSCON = 1; //Enable external oscilator

MC_ME.PCTL255.B.RUN_CFG = 0x0; //enable PWM in RUN_PC_0

MC_ME.PCTL251.B.RUN_CFG = 0x0; //enable ctu in RUN_PC_0

//AUX Clock Selector 3 setup

MC_CGM.AC3_SC.B.SELCTL =0x01; //connect (8..40MHz) XTALL to the PLL0 input

MC_ME.DRUN_MC.B.PLL0ON = 1; //Enable PLL0 for DRUN mode

//AUX Clock Selector 0 setup

MC_CGM.AC0_SC.B.SELCTL=0x2; //source PLL0 PHI 200MHz

MC_CGM.AC0_DC0.R = 0x80010000; //MOTC_CLK enable with divider 1

MC_CGM.AC0_DC2.R = 0x80010000; //ADC_CLK enable with divider 1

// Set PLL0 to 200MHz

PLLDIG.PLL0CR.B.CLKCFG = 1; //Bypass mode PLL0 on

// RFDPHI1 = 10, RFDPHI = 2, PREDIV = 2, MFD = 14

PLLDIG.PLL0DV.R = 0x50000000 |0x00020000 |0x00002000 |0x0014 ; //predefined PLL0 divider register

//Mode transition to apply the PLL0 setup and set Normal mode with PLL running

MC_ME.MCTL.R = 0x30005AF0; //DRUN Mode & Key

MC_ME.MCTL.R = 0x3000A50F; //DRUN Mode & Key

while(!MC_ME.GS.B.S_PLL0); //ME_GS Wait for PLL stabilization.

while(MC_ME.GS.B.S_MTRANS); //Waiting for end of transaction

while(MC_ME.GS.B.S_CURRENT_MODE != DRUN_MODE); // ME_GS Check DRUN mode has successfully been entered

}//Sys_Init

/*******************************************************************************

Function Name : SUIL2_Init

Engineer : b21190

Date : Mar-19-2015

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : SIUL2 initialization (ports), setting PB6(B9) as output for clock measurement

Issues : NONE

*******************************************************************************/

void SUIL2_Init(void)

{

SIUL2.MSCR[22].R = 0x22800001; //PB6 as CLK_OUT (on EVB it is B9)

/* setup ADC_0 channel AN0 as Analog Pad Control */

SIUL2.MSCR[23].B.APC = 0x1; //PB7 as AN0 (on EVB it is B0)

}//SUIL2_Init

/*******************************************************************************

Function Name : SWT_Init

Engineer : b21124

Date : MAR-17-2015

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : Initialize SWT

Issues : NONE

*******************************************************************************/

void SWT_Init(void)

{

/* Provide a Key to unlock SWT configuraiton registers */

SWT_0.SR.R = 0xC520;

SWT_0.SR.R = 0xD928;

/* Wait for solf-lock bit */

while (SWT_0.CR.B.SLK == 0x1);

/* Enable SWT_0 */

SWT_0.CR.B.WEN = 0x0;

/* Set SWT timeout */

SWT_0.TO.R = 0x000FFFFF;

SWT_0.CR.R = 0xFF000101;

}//SWT_Init

/*******************************************************************************

Function Name : FCCU_Init

Engineer : b21190

Date : Mar-30-2015

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : Configure FCCU fault reactions

Issues : NONE

*******************************************************************************/

void FCCU_Init(void)

{

/* Unlock configuration */

FCCU.TRANS_LOCK.B.TRANSKEY = 0xBC;

/* provide Config state key */

FCCU.CTRLK.R = 0x913756AF;

/* enter config state - OP1 */

FCCU.CTRL.R = 0x1;

/* Verify if state change was sucessful */

while (FCCU.CTRL.B.OPS != 0x3); //operation status successful

/* Configure FCCU to react on NCF with short reset */

FCCU.NCFS_CFG[0].B.NCFSC14 = 1; // see RM page 253 !!

//set up the NOMAL mode of FCCU

FCCU.CTRLK.R = 0x825A132B; //key for OP2

FCCU.CTRL.R = 0x2; //set the OP2 - set up FCCU into the NORMAL mode

while (FCCU.CTRL.B.OPS != 0x3); //operational status succesfull

}//FCCU_Init

/*******************************************************************************

Function Name : FCCU_clear_faults

Engineer : b21190

Date : Mar-12-2015

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : Example function for FCCU fault clearing

Issues : NONE

*******************************************************************************/

void FCCU_clear_faults(void)

{

/* 1. Write the proper key into the FCCU_NCFK register */

//Non-critical fault key = AB34_98FEh

FCCU.NCFK.R = 0xAB3498FE;

/* 2. Clear the status (flag) bit NCFSx => the opcode OP12 is automatically set into the FCCU_CTRL.OPR field */

/* Read all NCFS registers to clear all faults.*/

/* For details which faults can be cleared see Table 7-36. FCCU Non-Critical Faults Mapping in RM */

FCCU.NCF_S[0].R = 0xFFFFFFFF; // read FCCU.NCF_S0 register

/* Verify if state change was sucessful */

while (FCCU.CTRL.B.OPS != 0x3); //operation status succesfull

/* NCFS_1 register clear */

FCCU.NCFK.R = 0xAB3498FE; //Non-critical fault key = AB34_98FEh

FCCU.NCF_S[1].R = 0xFFFFFFFF; // clear FCCU.NCF_S1 register

/* Verify if state change was sucessful */

while (FCCU.CTRL.B.OPS != 0x3); //operation status succesfull

/* NCFS_2 register clear */

FCCU.NCFK.R = 0xAB3498FE; //Non-critical fault key = AB34_98FEh

FCCU.NCF_S[2].R = 0xFFFFFFFF; // clear FCCU.NCF_S2 register

/* Verify if state change was sucessful */

while (FCCU.CTRL.B.OPS != 0x3); //operation status succesfull

}//FCCU_clear_faults

int main(void)

{

volatile int counter = 0;

int i=0;

xcptn_xmpl (); /* Configure and Enable Interrupts */

Sys_Init();

SUIL2_Init();

FCCU_clear_faults();

FCCU_Init();

SWT_Init();

while (i==1)

{

FCCU_clear_faults();

}

while(1);

/* Loop forever */

for(;;) {

counter++;

}

}

******************************************

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

1. Thanks for pointing on SWT init function.

I have modified the example and enabled SWT. Now it works properly.

According to FCCU_clear fault routine, I call it because FCCU config state is accessible only if there is no latched fault in FCCU NCFSn registers.

I suggest you to first read my application notes such as http://cache.nxp.com/files/microcontrollers/doc/app_note/AN5284.pdf?fsrch=1&sr=2&pageNum=1

to get overview on the FCCU problematic.

Peter

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the fast reply.

I downloaded your modification, yet this is not the solution to our problem. Might be that your GHS project runs, but on S32ds it doesn’t.

You set WEN = 0x1 instead of 0x0 but actually we don’t even reach this point, the application hangs before that very line.

I attached our simple project s.t. you can have a quick look at it. I appreciate your help.

Thanks in advance

Lars

Von: petervlna

Gesendet: Mittwoch, 7. September 2016 13:40

An: Lars Krause

Betreff: Re: - Example MPC5744P SWT Short reset GHS614

NXP Community <https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg>

Example MPC5744P SWT Short reset GHS614

new comment by Peter Vlna<https://community.nxp.com/people/petervlna?et=watches.email.document_comment> View all comments on this document<https://community.nxp.com/docs/DOC-332499?commentID=37715&et=watches.email.document_comment#comment-37715>

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

I am not familiar with S32DS.

But my colleague told me that if you are using S32DS startups (I expect that you have written your custom one) then make sure that SWT periphery is not locked.

As S32DS is in startup locking access to SWT.

Peter

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi, Peter

I use Trace32 to debug the function of watchdog,I select MPC5744.cmm file when I run script.In the MPC5744.cmm,the option of SYStem Option.WATCHDOG is ON or OFF and why?In your example of SWT_short_reset,It's OFF.I appreciate your help.

Thanks in advance

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

This is the way how debugger write to WEN bit in SWT.

As you know debugger stops SWT when micro is in debug mode. In order to enable/disable SWT for debugging you can use this macro.

If you run this example standalone(without debugger connected) it just doesn't matter.

Peter

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello Peter,

I have implemented SWT0 on SPC5748G with this example code, but I have a question about FCCU initialization.

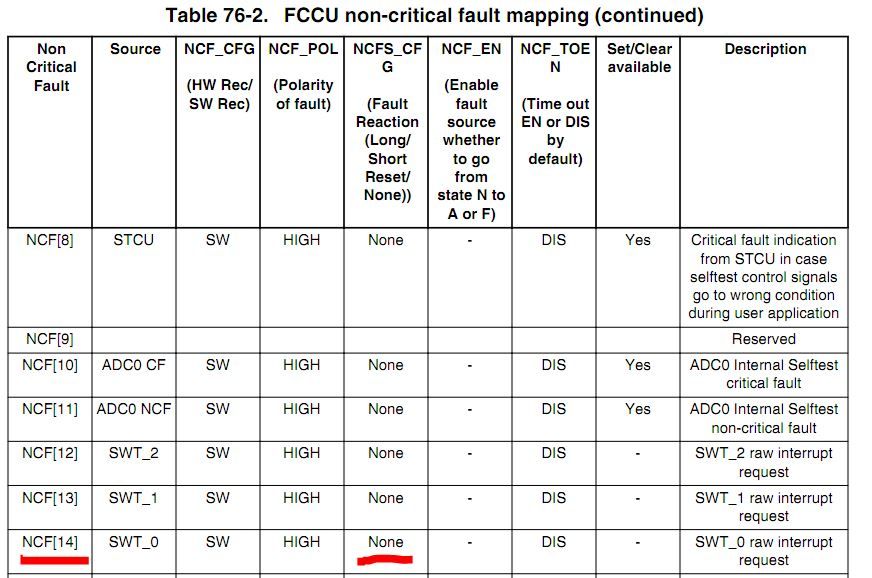

According to the SPC5748G RM, it describes that NCF[14] fault reaction is "None".

What is the exact meaning about this?

SWT0 of SPC5748G can report directly to the RGM without FCCU?

Best regards,

Neo

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

According to table reaction is None.

SWT is not directly wired to RGM module.

SWT timeout is wired to FCCU and FCCU is connected to RGM.

You have to configure FCCU in order to react on event coming form SWT.

Peter

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi, Peter

on S32ds it doesn’t run properly.

Although I have already put WEN = 0x1, SWT does not run properly, and time-out never happens.

How to make sure that SWT periphery is not locked?

Thanks

Lu

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi,

and what do you expect from example written for different compiler?

As I have already explained, if you use S32DS startup (and not your own) then you have to know what that startup does.

I prevents access to Watchdog from core. Set AIPS correctly and enable core access to peripheries like SWT.

Peter

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

HI,Peter

The reason that SWT does not run is known. FCCU is not started.

Short RESET can RESET to _start.

The problem now is that when Long RESET, it stops at the

;# Fill SRAM with writes of 32GPRs

sram_loop:

e_stmw r0,0(r5) # Write all 32 registers to SRAM

e_addi r5,r5,128 # Increment the RAM pointer to next 128bytes

e_bdnz sram_loop # Loop for all of SRAM

Long RESET is not RESET to _start?

Lu