- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MCX Microcontrollers

- :

- Not getting cpu frequency in IMX8ULP-EVK9

Not getting cpu frequency in IMX8ULP-EVK9

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Not getting cpu frequency in IMX8ULP-EVK9

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to change cpu frequency in A-Core of IMX8ULP-EVK9 with following commands given in user guide

echo 1 > /sys/device/platform/imx8ulp-lpm/enable

here is log I am getting

[ 470.247976] DDR enter low frequency mode

but I am unable to read current cpu-frequency by below commad

root@imx8ulp-9x9-lpddr4-evk:~# cpufreq-info

cpufrequtils 008: cpufreq-info (C) Dominik Brodowski 2004-2009

Report errors and bugs to cpufreq@vger.kernel.org, please.

analyzing CPU 0:

no or unknown cpufreq driver is active on this CPU

analyzing CPU 1:

no or unknown cpufreq driver is active on this CPU

and I don't have cpu_freq folder inside t /sys/devices/system/cpu/cpu0 or cpu1 I am using prebuilt linux image.

How can I get frequency and what is way to change it?

@Linux @imx8ulp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Chavira

Thanks for answer, i'm facing following issue to reduce A core frequency and accessing lpddr from M33 core.

Problem 1 :-

In my IMX8ULP-EVK 9 board I applied commad 'mhz' and I got 800MHz freq as an output than I applied 'echo 1 > /sys/device/platform/imx8ulp-lpm/enable' command and I got following log :- [ 470.247976] DDR enter low frequency mode.

Than again I checked freq with 'mhz' commad still I am getting 800MHz in that there is no change in frequency. Is there any other way to reduce frequency or it is the minimum one?

Problem 2 :-

I want to run A core at 200MHz so is there any way to configure clock at 200MHz for A core. I found following link to add particular clock settings in IMX8mp, IMX8mn etc.

How-to-reduce-the-CPU-Frequency-on-iMX8M

In this link they suggest to modify opp-table in imx8mm.dtsi file for selected board, but in imx8ulp.dtsi file we didn't find any opp-table entry. so we need to add opp-table entry manually? if yes so how can i, can you please share patch file for that.

Problem 3 :-

When i enter "echo mem > /sys/power/state" command on that time my A core and lpddr will be in deep sleep mode, but on same time M33 core need to access lpddr so it is possible to use lpddr from M33 core while A35 core in deep sleep mode? if yes, so how we can do?

Thanks

Dhruvin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @dhruvinrajpura!

1>> In the Linux reference manual only refer to the command to reduce the DDR frequency not the CPU frequency.

I recommend using the nominal mode bootloader and device tree to reduce the CPU frequency.

2>> The driver for iMX8MN is different than iMX8ULP, for a better understanding of power management of iMX8ULP I recommend to check the AN13914

3>> You can consult the AN13914 to see the available use cases for iMX8ULP.

https://www.nxp.com/docs/en/application-note/AN13914.pdf

Best Regards!

Chavira

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @Chavira

Question - 1

For earlier Problem 2

We gone throgh AN13914, Our goal is to reduce frequency of A core CPU upto 200MHz which is currently 800MHz (checked with command 'mhz')

To achieve that frequency, what changes we need to do in kernel space?

Question - 2

Currently we required to use PSRAM in code because internal SRAM is of 750Kb only, To check that whether we are acessing PSRAM correctly or not we initilized one buffer like below

'int __attribute__((section (".psram_data"))) psram_buffer[5000000];'

Is it possible that we are accessing PSRAM without initilizing it or it is initilizing from some different place already?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @dhruvinrajpura

For i.MX8ULP, the current BSP doesn't provide tool to change the cpu frequency, if we need to change the frequency, we can modify register value by using /unit-tests/memtool.

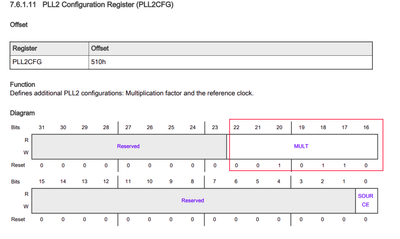

According to RM, from Chapter Clocking, we can know PLL2 is used exclusively for the A35, and in Chapter Clock Generation and Control(CGC1), there is a group of PLL2 registers, among them,

there is a division unit and a multiplication unit:

Overall, we can follow such steps to change the A core frequency:

- Switch a35 to another reference clock

- Modify PLLEN to 0

- Modify multiplication and division factors

- Modify PLLEN to 1

- Switch 35 back to PLL2

# Switch a35 to FRO 192 MHz

/unit_tests/memtool -32 0x292c0014=0x08000000

# Set PLLEN to 0

/unit_tests/memtool -32 0x292c0500=0x03000000

# Read and set the division and multiplication factors

/unit_tests/memtool -32 0x292c0014 1

/unit_tests/memtool -32 0x292c0510 1

# Set PLLEN to 1"

/unit_tests/memtool -32 0x292c0500=0x03000001

# Switch a35 to PLL2"

/unit_tests/memtool -32 0x292c0014=0x18000000

mhz

About of question 2, you can see the low_power_display.c example in the i.MX8ULP SDK:

boards\evkmimx8ulp\demo_apps\low_power_display

it demonstrates how to use CM33 core to do a triple buffer pan display with total i.MX8ULP SoC power around 90mW. In this demo, the display controller, MIPI DSI host is controlled by CM33 instead of Application Domain (A35 cores). The frame buffers are put into the external PSRAM through FlexSPI interfaces, this can keep the DDR in retention mode to save power. The display content refresh rate is limited to one fps, RTD domain will enter sleep mode to save power after updated the display buffer address every seconds.

Best regards,

Salas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @Alejandro_Salas

Your inputs worked for me and I am able to run A core of IMX8ULP on 192MHz which was 800MHz earlier.

With IMX8ULP I am using IMX93 as well, and in that I have same issue currently it is running on 1600MHz and I want to reduce it upto 200MHz,

As per your input of IMX8ULP I cheked reference manual of IMX93 but in that I am not able to find register with which I can change clock value can you tell me to reduce clock of IMX93 (A core) which register value I need to change?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @dhruvinrajpura

It is preferable to create a new thread about of the i.MX93 because this one is for i.MX8ULP, It is better for community search process.

Best regards,

Salas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @dhruvinrajpura!

Thank you for contacting NXP Support!

For iMX8ULP you can use the command "mhz" to see the CPU frequency, the command that you are using to enable the lpm is correct

Best Regards!

Chavira