- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- MCUXpresso SDK

- :

- IMXRT1060 USB Host MSD Example Fails to Enumerate When Using SDRAM

IMXRT1060 USB Host MSD Example Fails to Enumerate When Using SDRAM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMXRT1060 USB Host MSD Example Fails to Enumerate When Using SDRAM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone,

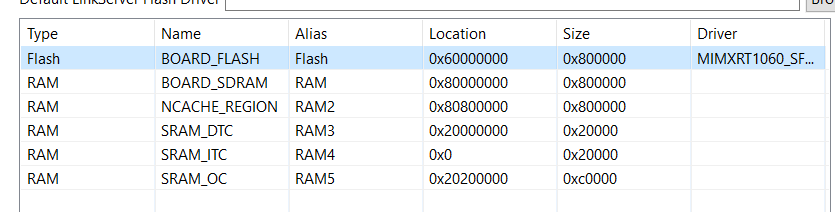

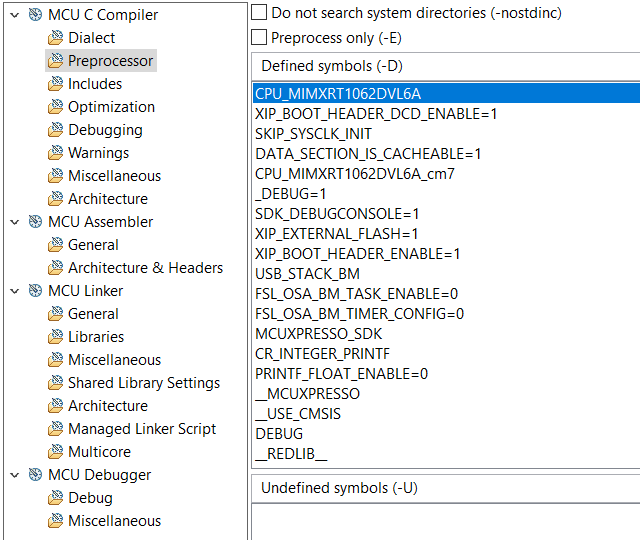

I was trying to get the USB Host MSD Command bare-metal example to work when using the external SDRAM. The example was modified to work with a custom board I have (added DCD to setup XIP w/ QSPI flash and SEMC for SDRAM, VBUS control), and the modified example works when using SRAM_DTC; my USB drive enumerates and the test executes successfully.

However, when I modify the example to use SDRAM instead of SRAM_DTC, my USB drive fails to enumerate. It appears that the stack doesn't receive any data, causing it to timeout the enumeration process.

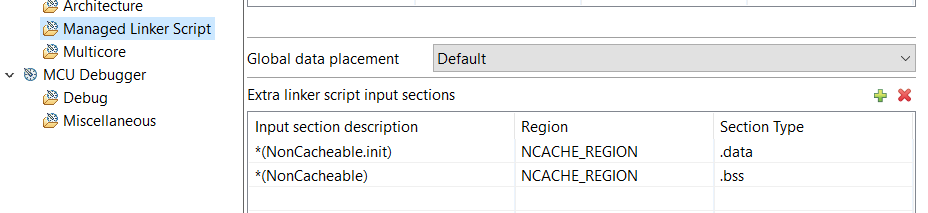

I had seen that other people had issues with parts of the SDK not working when buffers are located in cacheable memory, so I went through and updated my project based off the following posts, and I could see that some of the USB buffers moved to the non-cacheable region I defined in SDRAM. However, my drive still would not enumerate.

Using NonCached Memory on i.MXRT

MCUX on RT1050 - MMC stack won't initialize

IMXRT1050 USB DEVICE examples fail to run from OCRAM

My main question is: How can I get the USB stack to work with a non-cacheable section defined in SDRAM?

Below I've attached parts of my project setup in case I've missed something.

Many thanks,

jg_sung

Here are my modified MPU regions: I added region 13 (seems redundant b/c of region 10) and updated region 9's size to match my defined memory layout. The rest of the regions are original to the example.

/*

* Add default region to deny access to whole address space to workaround speculative prefetch.

* Refer to Arm errata 1013783-B for more details.

*

*/

/* Region 0 setting: Instruction access disabled, No data access permission. */

MPU->RBAR = ARM_MPU_RBAR(0, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_NONE, 0, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4GB);

/* Region 1 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 2 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Region 3 setting: Memory with Normal type, not shareable, outer/inner write back. */

MPU->RBAR = ARM_MPU_RBAR(3, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_8MB);

#endif

/* Region 4 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(8, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);

/* Region 9 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(9, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_8MB);

while ((size >> i) > 0x1U)

{

i++;

}

if (i != 0)

{

/* The MPU region size should be 2^N, 5<=N<=32, region base should be multiples of size. */

assert(!(nonCacheStart % size));

assert(size == (uint32_t)(1 << i));

assert(i >= 5);

/* Region 10 setting: Memory with Normal type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(10, nonCacheStart);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, i - 1);

}

/* Region 10 setting: Memory with Device type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(11, 0x40000000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4MB);

/* Region 12 setting: Memory with Device type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(12, 0x42000000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1MB);

/* Region 13 setting: Memory with non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(13, 0x80800000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_8MB);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @jg_sung ,

The USB MSD example can work with all data in SDRAM. The key is put all the buffer used by both hardware and software in noncacheable area. You must check them carefully.

https://community.nxp.com/t5/i-MX-RT/USB-Host-enumeration-fails/m-p/1436138

Regards,

Jing