- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpresso软件和工具

- :

- MCUXpresso IDE

- :

- Re: MCUXpresso Heap Usage (FreeRTOS) reporting problem when using Heap 5 memory scheme

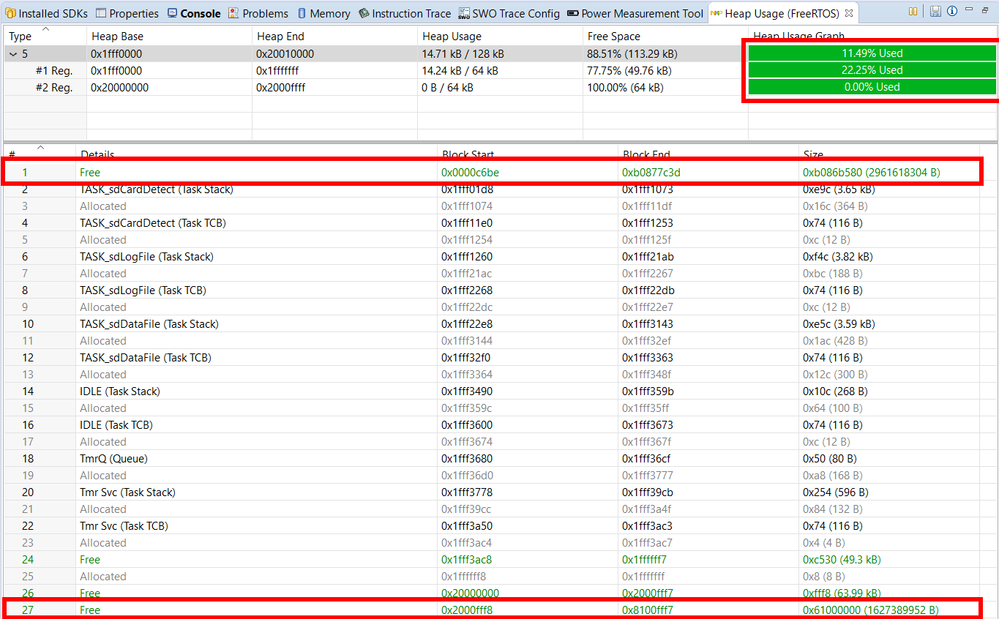

MCUXpresso Heap Usage (FreeRTOS) reporting problem when using Heap 5 memory scheme

Hi,

I'm using the MCUXpresso FreeRTOS SDK and switched over to the Heap 5 memory allocation scheme in order to use both memory regions on the MK22FN1M0VLK12 I'm using (64kB + 64kB).

However, I can no longer accurately analyse how the heap is being used as the Heap Usage table shows blocks that are not part of the heap and it is preventing the green/red bar visualisation from displaying properly.

I am getting a ~500MB block of memory being reported.

How can I fix this?

Thanks

已解决! 转到解答。

As previously stated, we are investigating this issue with the FreeRTOS TAD view. Hopefully we can incorporate a fix in the next IDE release.

Regards,

MCUXpresso IDE Support

Hi BlackNight,

Finally I'm able to reproduce the error!

This is the same project that was displaying correct data in the heap view: the only difference is that this project starts at address 0x10000 (there is a boot loader).

To make it work I inserted the following lines at the beginning of the ResetISR() function (startup_mk66f18.c file) to modify the VBR register to use the correct address of the interrupt vectors (as it was in the previous SDK version).

__asm volatile

(

"ldr r0, =0xE000ED08\n"

"ldr r1, =g_pfnVectors\n"

"str r1, [r0]\n"

"ldr r2, [r1]\n"

"msr msp, r2\n"

);

I hope this is useful to reproduce it on your side.

Many thanks,

Biafra

Hi Erich,

I'm trying to prepare what you asked for.

Isn't this problem related to the fact that one of the regions is in external RAM?

My configuration is:

static __NOINIT(FLEX_RAM) uint8_t HeapReagion1[ HEAP_REGION1_SIZE ];

static __NOINIT(SRAM_LOWER) uint8_t HeapReagion2[ HEAP_REGION2_SIZE ];

static __NOINIT(EXTRAM) uint8_t HeapReagion3[ HEAP_REGION3_SIZE ];

static const HeapRegion_t xHeapRegions[] =

{

{ HeapReagion1, HEAP_REGION1_SIZE },

{ HeapReagion2, HEAP_REGION2_SIZE },

{ HeapReagion3, HEAP_REGION3_SIZE },

{ NULL, 0 } //Terminates the array

};

EXTRAM is at address 0x90000000

Many thanks

Biafra

Hi Erich,

Sorry, but I can't share the project.

The heap memory configuration is as follows:

Region 1: start address -> 0x14000000, size 0x1000 (K66 internal FLEXRAM)

Region 2: start address -> 0x1FFF0000, size 0xF000 (K66 internal RAM lower bank)

Region 3: start address -> 0x900006A8, size 0x4E000 (external SRAM) (this region size is modified compared to the image I posted)

Many thanks

Biafra

Hi Erich,

I think the external SRAM is not needed: in the previous image, in the lower pane, the error is across two different memory blocks that are both internal, one in the lower bank and the other in the upper one.

There is another error (not shown in the image) that is across the upper internal bank and the external SRAM bank.

I don't think the problem is related to the external SRAM, I think it's related simply to the dual banks (heap 5 memory scheme).

Many thanks

Biafra

Thanks for your report. We'll investigate, but I suspect that the FreeRTSO TAD plugin doesn't currently support the use of FreeRTOS's heap5 option (span multiple non adjacent (non-contiguous) memory regions).

Regards,

MCUXpresso IDE Support

Thanks.

When do you think you'll get an answer on this please?

I think this feature is important as the MCUXpresso SDK supports all FreeRTOS memory schemes and you'd expect MCUXpresso IDE to do so too.

Otherwise, development slows down.