- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- Re: LS1043argw RGMII

LS1043argw RGMII

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LS1043argw RGMII

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have successfully built a custom board based on LS1043argw rev B. I'm using 2016.09+fslgit-r0 uboot files.

For the custom board, the here's the changes:-

1) not using sgmii in the architecture (hence no 4 port ethernet phy in the design), using 2 X RGMII instead using AR8035 atheros phy.

- Change rcw on bit 416 to 421 to 000000 (RGMII and RGMII2)

- Change rcw serdes protocol to 1555 (XFI, 3 x PCIE & RGMII) (hence, technically i don't have TSEC1, TSEC2, TSEC5, TSEC6 which belongs previously to RGW reference design having Vitesse phy), i still have 10G fibre optic configuration same as RGW reference design.

- On the changes on adding PCIE3 (since I choose serdes protocol 1555), i won't discuss here, coz want to discuss only the RGMII

- On schematic, 1 x atheros AR8035 (ethernet phy) is connected to EC1 = RGMII 1 having EMI1_MDC and EMI1_MDIO connected, having physical address 1

- another atheros AR8035 (ethernet phy) is connected to EC2 = RGMII 2 having EMI2_MDC and EMI2_MDIO connected having physcial address 2

- In the make menuconfig, i have enabled ethernet portion with the driver AR8035 enabled. uboot can recognise this driver as shown in uboot log below.

- In the ls1043argw.c file, i have added the line

fm_info_set_phy_address(FM1_DTSEC3, RGMII_PHY1_ADDR);

fm_info_set_phy_address(FM1_DTSEC4, RGMII_PHY2_ADDR);

- In the ls1043argw.h, i have added the line

#define RGMII_PHY1_ADDR 0x1

#define RGMII_PHY2_ADDR 0x2

- In the uboot log below, you can see that when I type mdio list, i can see only DTSEC3 recognised in uboot as AR8035 (which I can ping and flash software to nand without issue), but somehow I can't get RGMII2 (DTSEC4 enabled). The error says could not get PHY for FSL_MDIO0: addr 2

=>mdio list

FSL_MDIO0:

1 - AR8035 <--> FM1@DTSEC3

Here's a snapshot of the uboot

U-Boot SPL 2016.092.0+ga06b209 (Feb 15 2019 - 16:37:26)

Initializing DDR....

Applying DDR4 workaround ......

Trying to boot from NAND

U-Boot 2016.092.0+ga06b209 (Feb 15 2019 - 16:37:26 +0800)

SoC: LS1043AE Rev1.1 (0x87920011)

Clock Configuration:

CPU0(A53):1600 MHz CPU1(A53):1600 MHz CPU2(A53):1600 MHz

CPU3(A53):1600 MHz

Bus: 400 MHz DDR: 1600 MT/s FMAN: 500 MHz

Reset Configuration Word (RCW):

00000000: 08100010 0a000000 00000000 00000000

00000010: 15550002 80004002 e0106000 c1002000

00000020: 00000000 00000000 00000000 01030940

00000030: 00000000 00003004 00000096 00000001

Model: LS1043A RGW Board

Board: LS1043ARGW, boot from NAND

SERDES Reference Clocks:

SD1_CLK1 = 156.25MHZ, SD1_CLK2 = 100.00MHZ

I2C: ready

DRAM: Detected UDIMM Fixed DDR on board

2 GiB (DDR4, 32-bit, CL=11, ECC off)

Retimer:

Revision 0x03, ID 0x01

SEC0: RNG instantiated

PSCI: PSCI does not exist.

Waking secondary cores to start from ffd0d000

All (4) cores are up.

Using SERDES1 Protocol: 5461 (0x1555)

NAND: 512 MiB

MMC: FSL_SDHC: 0

In: serial

Out: serial

Err: serial

Assign to qe-tdm clk, rcwpmuxcr0=4311

Not a microcode

Net: Fman1: Uploading microcode version 108.4.23

Could not get PHY for FSL_MDIO0: addr 2

Failed to connect

Could not get PHY for FM_TGEC_MDIO: addr 1

Failed to connect

PCIe0: pcie@3400000 Root Complex: no link

PCIe1: pcie@3500000 Root Complex: no link

PCIe2: pcie@3600000 Root Complex: no link

FM1@DTSEC3 [PRIME], FM1@DTSEC4, FM1@TGEC1

Hit any key to stop autoboot: 0

=> printenv

baudrate=115200

bootargs=console=ttyS0,115200 root=/dev/ram0 earlycon=uart8250,mmio,0x21c0500

bootcmd=nand read $kernel_load $kernel_addr $kernel_size;bootm $kernel_load

bootdelay=10

console=ttyAMA0,38400n8

eth1addr=00:04:9F:04:65:11

eth2addr=00:04:9F:04:65:22

eth3addr=00:04:9F:04:65:33

eth4addr=00:04:9F:04:65:44

eth5addr=00:04:9F:04:65:55

eth6addr=00:04:9F:04:65:66

ethact=FM1@DTSEC3

ethaddr=00:04:9F:04:65:00

ethprime=FM1@DTSEC3

fdt_high=0xffffffffffffffff

fdtcontroladdr=ffc08600

fileaddr=a0000000

filesize=1fff5d3

fman_ucode=ffc29530

hwconfig=fsl_ddr:bank_intlv=auto

initrd_high=0xffffffffffffffff

ipaddr=192.168.0.3

kernel_addr=0x160000

kernel_load=0xa0000000

kernel_size=1fff5d3

kernel_start=0x61100000

loadaddr=0x80100000

mtdparts=mtdparts=60000000.nor:1m(nor_bank0_rcw),1m(nor_bank0_uboot),1m(nor_ban)

ramdisk_addr=0x800000

ramdisk_size=0x2000000

serverip=192.168.0.60

stderr=serial

stdin=serial

stdout=serial

Environment size: 1267/8188 bytes

=> mdio list

FSL_MDIO0:

1 - AR8035 <--> FM1@DTSEC3

FM_TGEC_MDIO:

=> mii info

PHY 0x01: OUI = 0x1374, Model = 0x07, Rev = 0x02, 1000baseX, HDX

=>

Kindly help, what other modifications in the file structure i need to do to enable RGMII2 (DTSEC4)? Many thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry correction on typo should be eth.c file:-

- In the eth.c file in ls1043argw folder, i have added the line

fm_info_set_phy_address(FM1_DTSEC3, RGMII_PHY1_ADDR);

fm_info_set_phy_address(FM1_DTSEC4, RGMII_PHY2_ADDR);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello kl h,

LS1043ARDB integrates two RGMII ports setting up as FM1_DTSEC3 and FM1_DTSEC4, you could do your porting based on board/freescale/ls1043ardb/eth.c.

I cannot find u-boot source code supporting ls1043argw, would you please attach your modified eth.c and ls1043argw.h? I will do some verification for you on my side.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi, if you need me to attach the screenshot of schematics on RGMII connections, let me know. But the RGMII 1 and RGMII 2 connections are exact same IC.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

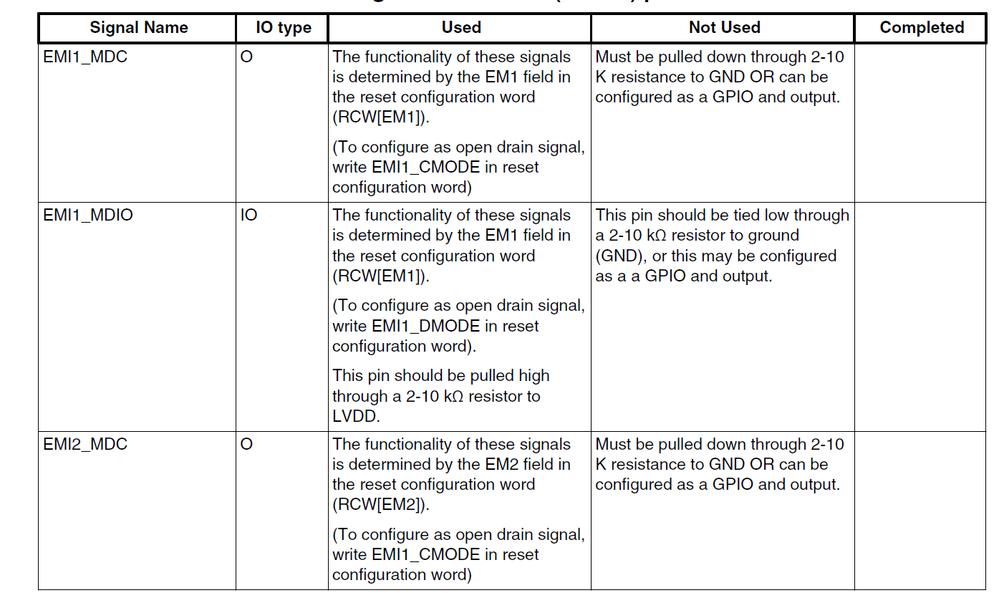

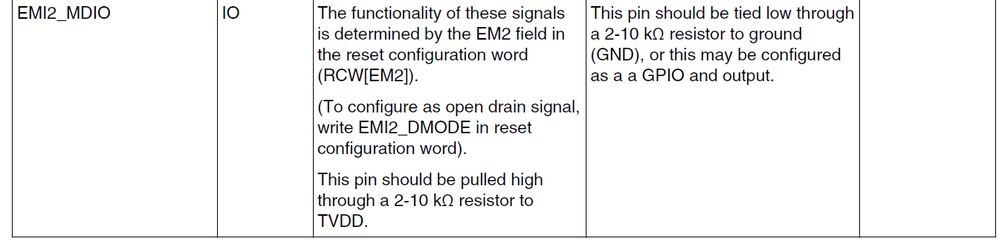

one more item, on the MDC and MDIO pins on the cpu, i have pull high of 1.5kohm and 4.7kohm. Maybe it's too high resistor value? Maybe I should reduce it to 200ohm and 330ohm... ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello kl h,

Please refer to the following section in Ethernet Management Interface (EMI1/2) pin termination checklist.

|

I didn't find obvious problem in your modified u-boot source code. Please check the hardware design.

Thanks,

Yiping

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

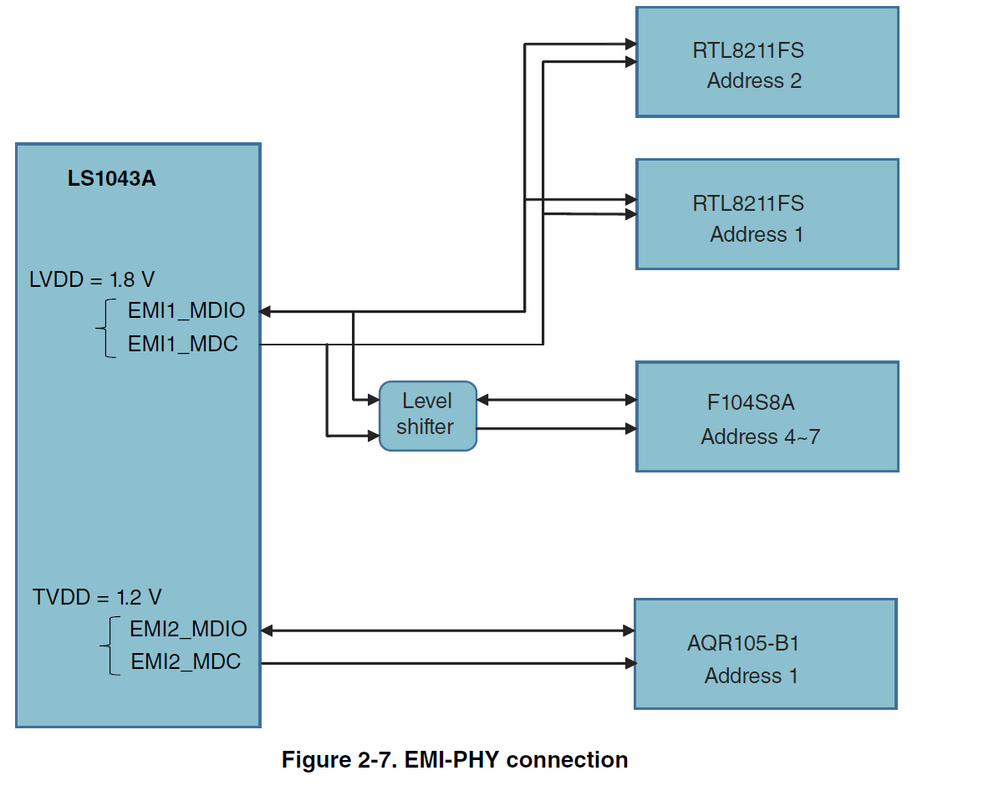

Hi Yi Ping,

Thanks for the lookup on the codes. I follow your advise and check on the hardware connections again. Apparently, during P1023, I use common mdc mdio from cpu to both the phy Ethernet @ address 1 & 2.

Here I further do the modification and connect both phy’s MDC and MDIO to EMI1_MDC and EMI1_MDIO. Now I don’t get the error anymore.

When I type mdio list, I get

FSL_MDIO0:

1 – AR8035 < - - > FM1@DTSEC3

2 – AR8035 < - - > FM1@DTSEC4

FM_TGEC_MDIO:

1 – Generic 10G PHY < - - > FM1@TGEC1

Hence, I think the code FSL_MDIO0 maybe referring to EMI1_MDC and EMI1_MDIO and not EMI2…

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello kl h,

Please also refer to LS1043ARDB hardware design as the following, RTL8211FS is RGMII PHY, AQR105-B1 is XFI PHY.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yi Ping,

Thanks for the detailed description. It’s very clear for my modification of the design. We can now close the thread.

Actually I have another question on the I2C portion, but should continue with this or raise a new Thread in the community?

regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello kl h,

Please create a new thread in community to address you other issue to make it convenient for other customers to searching from.

Thanks,

Yiping