- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1012A QSPI-Flashing Problem on Custom Board

LS1012A QSPI-Flashing Problem on Custom Board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LS1012A QSPI-Flashing Problem on Custom Board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

We are trying to flash the default RCW to QSPI on our custome board based on "LS1012AXN7EKB". We have followed the referance schematics of " LS1012A-FRDM".

H/W Settings (Hardcoded - RCW)

CPU Part Number : LS1012AXN7EKB

cfg_sysclk_sel (QSPI_A_CS0) -- Pull Down

cfg_func_backup (QSPI_A_DATA1) -- Pull Down

cfg_eng_use -- Pull-Up

cfg_eng_use2 -- Pull-Up ( we are using External Clk)

cfg_rcw_src -- Pull-Down

Target Initialization Script:

USE_SAFE_RCW = True

we are getting the following error

/***************************************************************/

ERROR: Memory access failed.

//

Additional error details:

Failed to write memory at address 0x1ee00e4 on core CortexA53#0.

Core CortexA53#0 not found on the JTAG chain. Please verify that the Reset Configuration Word is correct, or enable RCW Override in the initialization file.

/***************************************************************/

H/W Settings (QSPI - RCW)

cfg_sysclk_sel (QSPI_A_CS0) -- Pull Down

cfg_func_backup (QSPI_A_DATA1) -- Pull Down

cfg_eng_use -- Pull-Up

cfg_eng_use2 -- Pull-Up ( we are using External Clk)

cfg_rcw_src -- Pull-Up (QSPI Selected)

Target Initialization Script:

USE_SAFE_RCW = False

We have witten the RCW values to QSPI flash using External programmer.

RCW Values for your Ref

/********************************************************************/

00000000: aa 55 aa 55 01 ee 01 00 08 00 00 06 00 00 00 00

00000010: 00 00 00 00 00 00 00 00 33 05 00 00 c0 00 00 0c

00000020: 40 00 00 00 00 00 18 00 00 00 00 00 00 00 00 00

00000030: 00 00 00 00 00 0c 47 f2 00 00 00 00 10 c2 a1 20

00000040: 00 00 00 96 00 00 00 00 09 55 00 00 00 0f 40 0c

00000050: 09 57 06 04 40 10 00 00 09 57 01 5c 50 10 00 00

00000060: 09 57 06 00 00 00 00 00 08 61 00 40 33 52 b6 69

/********************************************************************/

/********************************************************************/

0-1 SYS_PLL_CFG 2'h00 (0b00 - For all valid Platform PLL frequencies)

2-6 SYS_PLL_RAT 5'h04 (0b00100 - 4:1)

7-7 RESERVED_7 1'h00 (0b0 - Default value)

8-9 RESERVED_9_8 2'h00 (0b00 - Default value)

10-15 RESERVED_15_10 6'h00 (0b000000 - Default value)

16-23 RESERVED_16_23 8'h00 (0b00000000 - Default value)

24-25 CGA_PLL1_CFG 2'h00 (0b00 - For all Cluster PLL frequencies)

26-31 CGA_PLL1_RAT 6'h06 (0b000110 - 6:1 (Aync Mode))

32-33 RESERVED_33_32 2'h00 (0b00 - Default value)

34-39 RESERVED_39_34 6'h00 (0b000000 - Default value)

40-47 RESERVED_40_47 8'h00 (0b00000000 - Default value)

48-49 RESERVED_49_48 2'h00 (0b00 - Default value)

50-55 RESERVED_55_50 6'h00 (0b000000 - Default value)

56-57 RESERVED_57_56 2'h00 (0b00 - Default value)

58-63 RESERVED_63_58 6'h00 (0b000000 - Default value)

64-71 RESERVED_64_71 8'h00 (0b00000000 - Default value)

72-73 RESERVED_73_72 2'h00 (0b00 - Default value)

74-79 RESERVED_79_74 6'h00 (0b000000 - Default value)

80-81 RESERVED_81_80 2'h00 (0b00 - Default value)

82-87 RESERVED_87_82 6'h00 (0b000000 - Default value)

88-95 RESERVED_88_95 8'h00 (0b00000000 - Default value)

96-99 C1_PLL_SEL 4'h00 (0b0000 - CGA_PLL1 / 1)

100-103 RESERVED_103_100 4'h00 (0b0000 - Default value)

104-107 RESERVED_107_104 4'h00 (0b0000 - Default value)

108-111 RESERVED_111_108 4'h00 (0b0000 - Default value)

112-115 RESERVED_115_112 4'h00 (0b0000 - Default value)

116-119 RESERVED_119_116 4'h00 (0b0000 - Default value)

120-127 RESERVED_122_127 8'h00 (0b00000000 - Default value)

128-143 SRDS_PRTCL_S1 16'h3305 (0b0011001100000101)

144-151 RESERVED_144_151 8'h00 (0b00000000 - Default value)

152-157 RESERVED_152_157 6'h00 (0b000000 - Default value)

158-159 RESERVED_158 2'h00 (0b00 - Default value)

160-160 SRDS_PLL1_REF_CLK_SEL_S1 1'h01 (0b1 - For 1.25 or 2.5 or 5 GHz or 3 Ghz or 6 GHz Protocols: 125 MHz Note: If Serdes clock is provided internally, then 125 MHz setting must be used.)

161-161 SRDS_PLL2_REF_CLK_SEL_S1 1'h01 (0b1 - For 3.125 Gbps or 10 Gbps Protocols: 156.25 MHz For 1.25 or 2.5 or 5 GHz or 3 Ghz Protocols: 125 MHz Note: If Serdes clock is provided internally, then 125 MHz setting must be used.)

162-167 RESERVED_162_167 6'h00 (0b000000 - Default value)

168-169 SRDS_PLL_PD_S1 2'h00 (0b00 - PLL1 and PLL2 are not powered down.)

170-175 RESERVED_170_175 6'h00 (0b000000 - Default value)

176-177 RESERVED_176 2'h00 (0b00 - Default value)

178-183 RESERVED_178_183 6'h00 (0b000000 - Default value)

184-184 RESERVED_184 1'h00 (0b0 - Default value)

185-185 RESERVED_185 1'h00 (0b0 - Default value)

186-187 RESERVED_186_187 2'h00 (0b00 - Default value)

188-188 SRDS1_REFCLK_SEL 1'h01 (0b1 - Single reference clock to both PLLs)

189-189 SRDS1_INT_REFCLK 1'h01 (0b1 - Internal differential reference clock (125 MHz) is used)

190-191 RESERVED_190_191 2'h00 (0b00 - Default value)

192-195 PBI_SRC 4'h04 (0b0100 - QSPI)

196-200 RESERVED_196_200 5'h00 (0b00000 - Default value)

201-201 BOOT_HO 1'h00 (0b0 - Core not in holdoff)

202-202 SB_EN 1'h00 (0b0 - Secure boot is not enabled)

203-223 RESERVED_212_223 21'h00 (0b000000000000000000000 - Default value)

224-232 RESERVED_224_231 9'h00 (0b000000000 - Default value)

233-233 RESERVED_233 1'h00 (0b0 - Default value)

234-234 RESERVED_234 1'h00 (0b0 - Default value)

235-241 RESERVED_235_241 7'h00 (0b0000000 - Default value)

242-243 SYS_PLL_SPD 2'h01 (0b01 - Default)

244-244 CGA_PLL1_SPD 1'h01 (0b1 - Low-speed operation ()

245-245 RESERVED_245_245 1'h00 (0b0 - Default value)

246-255 RESERVED_246_255 10'h00 (0b0000000000 - Default value)

256-259 RESERVED_256_259 4'h00 (0b0000 - Default value)

260-262 RESERVED_262_260 3'h00 (0b000 - Default value)

263-263 RESERVED_263_263 1'h00 (0b0 - Default value)

264-264 HOST_AGT_PEX 1'h00 (0b0 - Host Mode)

265-266 RESERVED_265_266 2'h00 (0b00 - Default value)

267-267 RESERVED_267 1'h00 (0b0 - Default value)

268-268 RESERVED_268_268 1'h00 (0b0 - Default value)

269-287 RESERVED_269_287 19'h00 (0b0000000000000000000 - Default value)

288-319 GP_INFO_288_319 32'h00 (0b00000000000000000000000000000000 - Default value)

320-351 RESERVED_320_351 32'h00 (0b00000000000000000000000000000000 - Default value)

352-353 RESERVED_352_353 2'h00 (0b00 - Default value)

354-354 SDHC2_EXT_CLK 1'h00 (0b0 - GPIO1(29))

355-355 SDHC2_EXT_CMD 1'h00 (0b0 - GPIO1(24))

356-356 SDHC2_EXT_DAT3 1'h00 (0b0 - GPIO1(28))

357-357 SDHC2_EXT_DAT2 1'h00 (0b0 - GPIO1(27))

358-358 SDHC2_EXT_DAT1 1'h00 (0b0 - GPIO1(26))

359-359 SDHC2_EXT_DAT0 1'h00 (0b0 - GPIO1(25))

360-361 EC1_EXT_SAI3 2'h00 (0b00 - GPIO2(3), GPIO2(11), GPIO2(12))

362-363 EC1_EXT_SAI4 2'h00 (0b00 - GPIO2(2), GPIO2(13), GPIO2(14))

364-364 EC1_EXT_SAI2_TX 1'h01 (0b1 - SAI2_TX_DATA, SAI2_TX_SYNC, SAI2_TX_BCLK)

365-365 EC1_EXT_SAI2_RX 1'h01 (0b1 - SAI2_RX_DATA, SAI2_RX_SYNC, SAI2_RX_BCLK)

366-367 EC1_BASE 2'h00 (0b00 - See EC1_EXT_* bit definition)

368-369 UART1_BASE 2'h01 (0b01 - UART1_SOUT, UART1_SIN)

370-371 UART2_FLOW_BASE 2'h00 (0b00 - GPIO1(7), GPIO1(9), GPIO1(10))

372-373 SDHC1_BASE 2'h01 (0b01 - SDHC1_CMD, SDHC1_DAT(3:0), SDHC1_CLK)

374-375 SDHC2_DAT321_BASE 2'h03 (0b11 - SPI_MISO, SPICS2_B, SPI_CS1_B)

376-377 SDHC2_BASE_BASE 2'h03 (0b11 - SPI_MOSI, SPICS0_B, SPI_CLK)

378-378 UART2_DATA_BASE 1'h01 (0b1 - UART2_SOUT, UART2_SIN)

379-379 EMI1_BASE 1'h01 (0b1 - EMI1_MDC, EMI1_MDIO)

380-381 GPIO_FTM_EXTCLK_BASE 2'h00 (0b00 - GPIO1(30))

382-383 CLK_OUT_BASE 2'h02 (0b10 - RESET_REQ_B)

384-404 RESERVED_384_404 21'h00 (0b000000000000000000000 - Default value)

405-415 RESERVED_405_415 11'h00 (0b00000000000 - Default value)

416-418 RESERVED_416_418 3'h00 (0b000 - Default value)

419-419 SDHC1_CD 1'h01 (0b1 - SDHC1_CD_B)

420-420 SDHC1_WP 1'h00 (0b0 - GPIO1(22))

421-421 QSPI_DATA0_GPIO 1'h00 (0b0 - QSPI_A_DATA0, QSPI_A_SCK, QSPI_A_CS0)

422-423 QSPI_DATA1_GPIO 2'h00 (0b00 - QSPI_A_DATA1)

424-425 QSPI_IIC2 2'h03 (0b11 - GPIO1(13), RESET_REQ_B)

426-428 RESERVED_426_428 3'h00 (0b000 - Default value)

429-430 USB1_DRVVBUS_BASE 2'h01 (0b01 - USB1_DRVVBUS)

431-432 USB1_PWRFAULT_BASE 2'h01 (0b01 - USB1_PWRFAULT)

433-433 RESERVED_433 1'h00 (0b0 - Default value)

434-434 SDHC1_VSEL 1'h01 (0b1 - SDHC1_VSEL)

435-437 RESERVED_435_437 3'h00 (0b000 - Default value)

438-438 EMI1_DMODE 1'h00 (0b0 - MDIO configured in normal functional mode.)

439-440 EVDD_VSEL 2'h02 (0b10 - 3.3V)

441-442 IIC1_BASE 2'h01 (0b01 - IIC1_SCL, IIC1_SDA)

443-443 RESERVED_443 1'h00 (0b0 - Default value)

444-444 EMI1_CMODE 1'h00 (0b0 - MDC configured in normal functional mode.)

445-447 RESERVED_445_447 3'h00 (0b000 - Default value)

448-471 RESERVED_448_471 24'h00 (0b000000000000000000000000 - Default value)

472-481 SYSCLK_FREQ 10'h258 (0b1001011000 - 100 MHz)

482-508 RESERVED_482_508 27'h00 (0b000000000000000000000000000 - Default value)

509-511 RESERVED_511_509 3'h00 (0b000 - Default value)

/********************************************************************/

we are getting the following error

/***************************************************************/

ERROR: PBL phase completed with error 'No preamble is detected'

Failed to execute target initialization script

/***************************************************************/

Any help finding the problem is appreciated. Let us know is any more information required.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello srikanth reddy,

Please refer to https://community.nxp.com/message/852508?commentID=852508#comment-852508

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

We have tried the procedure you have given us, to get our custom board to boot. CWTAP is failing to initialize the target. These are the following messages

GNU gdb (GDB) 7.11.1.0.3f0b3f2-b180725 (NXP Semiconductors)

Copyright (C) 2016 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law. Type "show copying"

and "show warranty" for details.

This GDB was configured as "--host=mingw32 --target=aarch64-fsl-linux".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

<http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word".

(gdb) source ../../gdb_extensions/flash/cwflash.py

Starting flash programmer services...

Starting local server...

Successfully started gdb server 127.0.0.1:45001.

Set gdb remote timeout to 7200

Connecting to target...

Using LS1012A SoC

Using CWTAP 00:04:9f:04:cc:34

Using jtag speed 6000

Connecting to probe...

connected successfully

Successfully connected to probe

Initializing target...

Running init script c:\freescale\cw4net_v2019.01\cw_armv8\armv8\gdb_extensions\flash\scripts/../../../../Config/boards/LS1012A_FRDM_init.py

RCW error encountered. In order to diagnose the error temporarily change the board configuration switches to ignore the assertion of the RESET_REQ_B signal. Please refer to board reference manual in order to locate the appropriate switch that controls this behavior.

Error: fail to initialize target

Closing debugger server...

Error: fail to start flash programming services.

(gdb)

We are pasting "cwflash.py".

###################################################################

######### Parameters

###################################################################

# Board type (Supported values: "QDS", "RDB").

BOARD_TYPE = "FRDM"

# Flash types (Supported values: "nor", "nand", "qspi", "sd", "mmc").

FLASH_TYPE = "qspi"

# Connection probe. Possible values:

# PROBE_CONNECTION = "" - use local CWTAP through USB.

# PROBE_CONNECTION = "<serial_number>" - use local CWTAP USB with specified serial number. Ex: "12:34:56:78:9a:bc"

# PROBE_CONNECTION = "<IP>|<host_name>" - use remote CWTAP

# PROBE_CONNECTION = "cmsisdap[:<serial_number>]" - use CMSIS-DAP with or without serial number

#PROBE_CONNECTION = "cmsisdap:COM10"

PROBE_CONNECTION = "00:04:9f:04:cc:34"

# Current SoC name.

SOC_NAME = "LS1012A"

# JTAG speed.

# For CMSIS-DAP please lower the JTAG speed to 6000.

JTAG_SPEED = 6000

# Address:port (IP/host name:port) where CCS is located.

# If empty, it will use local connection.

# Ex: 127.0.0.1:41475

CCS_CONNECTION = ""

# Address:port that will be used by GTA.

# If empty, it will use local connection.

# Ex: 127.0.0.1:45000

GTA_CONNECTION = ""

# Remote target responses timeout (seconds).

GDB_TIMEOUT = 7200

###################################################################

######### Start Flash Programming Services

###################################################################

import sys

import os

#compute gdb_extensions absolute path

FLASH_EXT_INSTALL_DIR = ''.join([os.path.dirname(os.path.realpath(__file__)), '/'])

GDB_EXT_INSTALL_DIR =''.join([FLASH_EXT_INSTALL_DIR, '../'])

#add gdb_extensions to system path

sys.path.insert(0, GDB_EXT_INSTALL_DIR)

from flash.scripts.services import start_fp_services

def fp_initialization():

"""

CodeWarrior services initialization script

"""

gtaip = GTA_CONNECTION

ccsip = CCS_CONNECTION

dev_arg = '-d %s' % FLASH_TYPE

soc_arg = '-s %s' % SOC_NAME

board_arg = '-b %s' % BOARD_TYPE

conn_arg = ''

if PROBE_CONNECTION:

conn_arg = '--probe %s' % PROBE_CONNECTION

# for CCS server to be started on host leave empty

ccsip_arg = ''

if ccsip:

ccsip_arg = '--ccsip %s' % ccsip

gtaip_arg = ''

if gtaip:

gtaip_arg = '--gtaip %s' % gtaip

jtag_speed_arg = '--jtag_speed %d' % JTAG_SPEED

timeout_arg = '--timeout %d' % GDB_TIMEOUT

argument = ' '.join([dev_arg, soc_arg, board_arg, conn_arg, ccsip_arg, \

gtaip_arg, jtag_speed_arg, timeout_arg])

start_fp_services(argument)

fp_initialization()

---------------------------------------------------------------------------------------------------------------------------------------------------------

we have checked USE_SAFE_RCW = False and USE_SAFE_RCW = True in "LS1012A_FRDM_init.py" .

Can you please check and let us know.

Thanks a lot.

Best Regards,

Srikanth Reddy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Srikanth Reddy,

Please configure the target board in hard-coded RCW mode.

Please configure cfg_rcw_src as 0 to configure the target board as hard-coded RCW, then use the procedure which I mentioned previously.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

Thanks a lot for the reply and sorry for the late response.

The cfg_rcw_src is configured to 0. We are getting the same errors.

We are trying to check few signals in our hardware.

Is there any test we can do using the CWTAP to make sure the processor and the other peripheral are good.

Best Regards,

Srikanth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

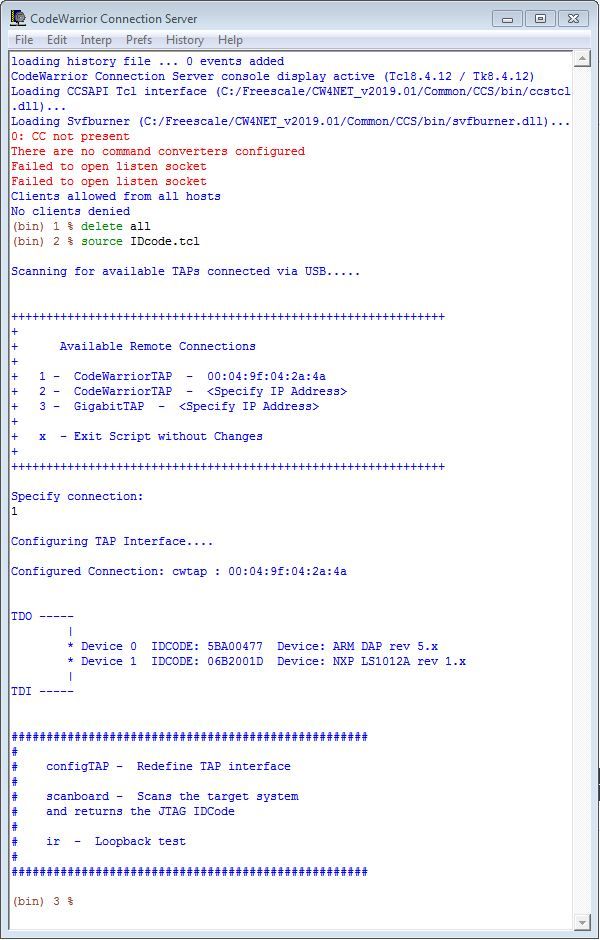

Hello Srikanth,

Please check whether the CCS can connect to the target processor through CodeWarrior TAP. Please open ccs.exe in C:\Freescale\CW4NET_v2020.06\Common\CCS\bin\, then type the following commands.

(bin) 3 % delete all

(bin) 5 % source IDcode.tcl

Scanning for available TAPs connected via USB.....

++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

+

+ Available Remote Connections

+

+ 1 - CodeWarriorTAP - 00:04:9f:04:2b:fa

+ 2 - CodeWarriorTAP - <Specify IP Address>

+ 3 - EthernetTAP - <Specify IP Address>

+ 4 - GigabitTAP - <Specify IP Address>

+

+ x - Exit Script without Changes

+

++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Specify connection:

1

Configuring TAP Interface....

Configured Connection: cwtap : 00:04:9f:04:2b:fa

TDO -----

|

* Device 0 IDCODE: 0000808F Device: Unknown Device

|

TDI -----

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yipingwang,

Thanks a lot for the reply. We have executed the procedure in ccs.exe which you have given.

This is the screenshot of the execution.

Best Regards,

Srikanth

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

Thanks a lot for the reply. We will check this soon as our board is having problem with the QSPI clk signal. We are trying to rectify that. Will let you know as soon as we check this.

Best Regards,

Srikanth Reddy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We get the same questions as yours, can you tell me yours solutions.

best wish ,thank you