- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: DDR4 RDIMM Bringup in LS2088A

DDR4 RDIMM Bringup in LS2088A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DDR4 RDIMM Bringup in LS2088A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Team,

We are using RDIMM DDR4 VL33A2G63F-N7SC , how to debug it further below is the logs booting stopped at uboot

Reset Configuration Word (RCW): 00000000: 402828b0 28280040 00000000 00000000 00000010: 00000000 00000000 00200000 00000000 00000020: 020011a0 00002580 00000000 00000000 00000030: 00000908 00000000 00000000 00000000 00000040: 00000000 00000000 00000000 00000000 00000050: 00000000 00000000 00000000 00000000 00000060: 00000000 00000000 0001b000 00000000 00000070: 3f370000 00010008 Board: LS2088AE Rev1.1-RDB, Board Arch: V15, Board version: P, boot from invalid setting of SW6 FPGA: v255.255 SERDES1 Reference : Clock1 = 156.25MHz Clock2 = 156.25MHz SERDES2 Reference : Clock1 = 100MHz Clock2 = 100MHz I2C: ready DRAM: Initializing DDR....using SPD Detected RDIMM VL33A2G63F-N7SC Detected RDIMM VL33A2G63F-N7SC DP-DDR: Not detected31.9 GiB DDR 31.9 GiB (DDR4, 64-bit, CL=10, ECC on) DDR Controller Interleaving Mode: 256B DDR Chip-Select Interleaving Mode: CS0+CS1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping,

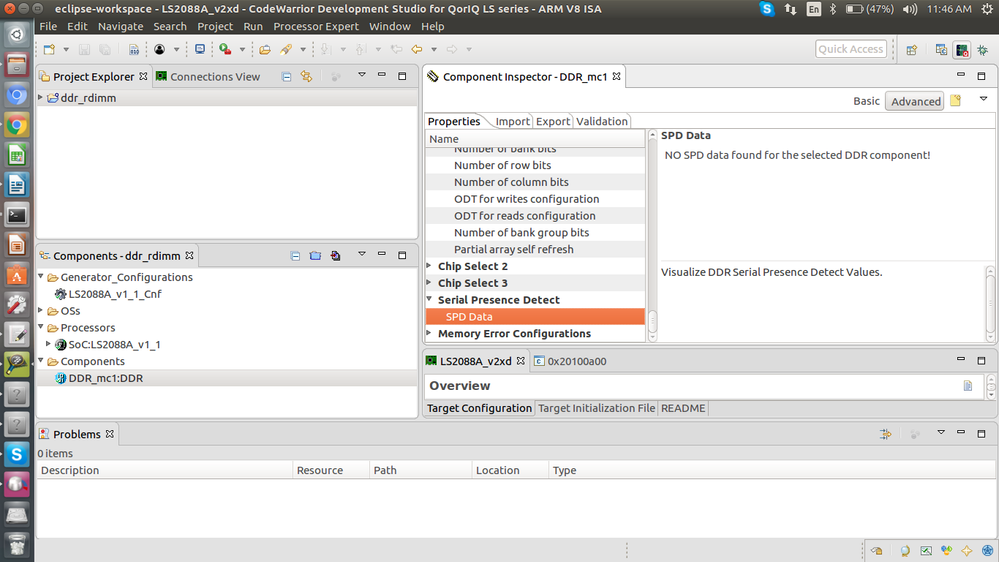

We are able to read SPD but we are not able apply SPD data in QCVS project attaching reference

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello pradeep TG,

When create a QCVS DDR project, please select the configuration mode as "Read SPD" in DDR configuration panel, after click "Read SPD" to connect to the target board to read SPD from the target board successfully, please follow the new project wizards to continue to create QCVS project. Then the initial DDR controller configuration parameters will be generated according to values reading from SPD.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello pradeep TG,

If you use new type DDRs on LS2088ARDB, you need to use QCS(DDRv) tool to connect to the target board do optimization and validation to get the optimized board specific parameters clk_adjust, wrlvl_start, wrlvl_ctl, and modify board_specific_parameters table defined in board/freescale/ls2080ardb/ddr.h in u-boot.

You could refer to the procedure described inDDR Controller Configuration on LS2085/LS2080 Bringing up .

The attached is QCVS DDRv tool user manual.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping,

Thank you for the support,

We are able to read SPD data from RDIMM, one issue we are facing is in QCVS tool after reading SPD data its showing Unsupported raw card revision. Set the CLK to DQS skew values manually. can you tell us how to calculate these values