- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: Bad data hash on QSPI on LS1043A (Yocto Tiny)

Bad data hash on QSPI on LS1043A (Yocto Tiny)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Platform: LS1043A

LSDK: LSDK 20.12

I have 7 target boards. I programmed with the same image to these 7 target boards. Everything works well under SDboot for all 7 boards, but not for QSPI Yocto tiny.

I used the command "flex-builder -i mkfw -m ls1043ardb -b sd" to generate the uboot enviroment. Then flash QSPI with the image that using ”flex-builder -I mkfw -m ls1043ardb -b qspi”. But when I start to run Yocto tiny, there are 3 different test results below on these 7 target boards.

1. 4 boards: getting "bad data hash" issue on Kernel image

2. 1 board: it's normal on Kernel image, but it also got "bad data hash" when it went to ramdisk image

3. 2 boards: It can successfully run Yocto tiny.

How can I fix these issues?

Please see attached for the log file and ls1043ardb_tfa_defconfig file for these 3 test results.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to your test result, it seems that there is problem with DDR controller initialization.

Please use QCVS DDRv tool to connect to your target board to do optimization and validation.

You also could define CONFIG_CMD_MEMTEST=y in configs/ls1043ardb_tfa_defconfig in u-boot source code, rebuild u-boot image and use mtest under u-boot to test DDR memory.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please do the following verification.

1. Please download pro-built image lsdk2012_yocto_tiny_LS_arm64.itb.

wget https://www.nxp.com/lgfiles/sdk/lsdk2012/lsdk2012_yocto_tiny_LS_arm64.itb

2. Please write image to offset 0x1000000 on QSPI flah.

tftp 0xa0000000 nxa22585/ls1046ardb/lsdk2012_yocto_tiny_LS_arm64.itb

sf probe 0:0

sf write 0xa0000000 0x1000000 0x2800000

3. Read image from offset 0x1000000 on QSPI flash.

sf read 0xa0000000 0x1000000 0x2800000

4. boot image.

bootm 0xa0000000#ls1043ardb

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

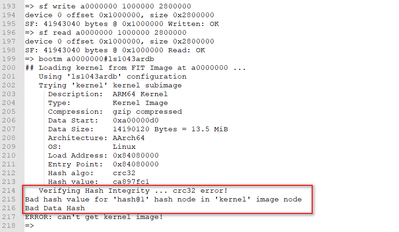

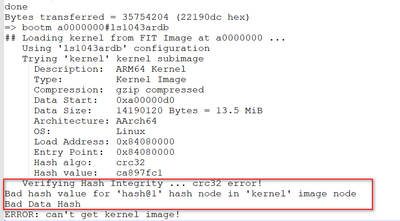

I run the tests as follows:

1. Followed your suggestion which flash the QSPI with pre-build image and write to the DDR from QSPI to run Yocto tiny.

=> the log of "QSPI_YOCTO_TINY.txt" shows it's still "bad data hash"

2. Read the data content of itb to DDR(0xa0000000) then bootm a0000000#ls1043ardb

=> the log of "DDR_YCOTO_TINY.txt" shows it's still "bad data hash"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to your test result, it seems that there is problem with DDR controller initialization.

Please use QCVS DDRv tool to connect to your target board to do optimization and validation.

You also could define CONFIG_CMD_MEMTEST=y in configs/ls1043ardb_tfa_defconfig in u-boot source code, rebuild u-boot image and use mtest under u-boot to test DDR memory.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I fine-tune the DDR timing again and flash SD/QSPI/eMMC with this new timing setting, it turns out to normally run linux kernel under all boot source for all boards.

But I used "mtest f8000000 ffffffff" to run DDR test, then found a failure happened and it's fixed at the address of F800,0000~FFFF,FFFF (the final 128MB) for all boards.

Is it possible that the MPU is using this range to access data while running DDR checking to fail the DDR checking?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please test DDR address range a0000000 to afffffff used in the testing procedure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I already run the test which includes whole range first and then narrow down to f8000000 ffffffff to make sure all is good except for this zone.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please load image from SD card to RAM to check whether it is bootable from RAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have run the DDR tests below and the test results should turn out the current DDR on target board works normally.

1. Run DDR test at Uboot mode on LS1046ARDB => it has the same test result which failed at the final 128MB. That proved the root cause is the MPU is using this zone while sweeping the address of DDR to fail the DDR test.

2. Run DDR test at kernel on our target board => there is no failure detected

Anyway, after we fine-tune the DDR configuration with increasing comparsion size on QVCS DDR tool, all the target boards work well under any boot source.

Many thanks for your support.