- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- how to use SPI

how to use SPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

how to use SPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Customer,

You can use the interrupt mode, it's no problem.

Now, answer your question:

Take the sdk code SDK_2.3.0_LPCXpresso54608\boards\lpcxpresso54608\driver_examples\spi\interrupt_b2b\master as an example.

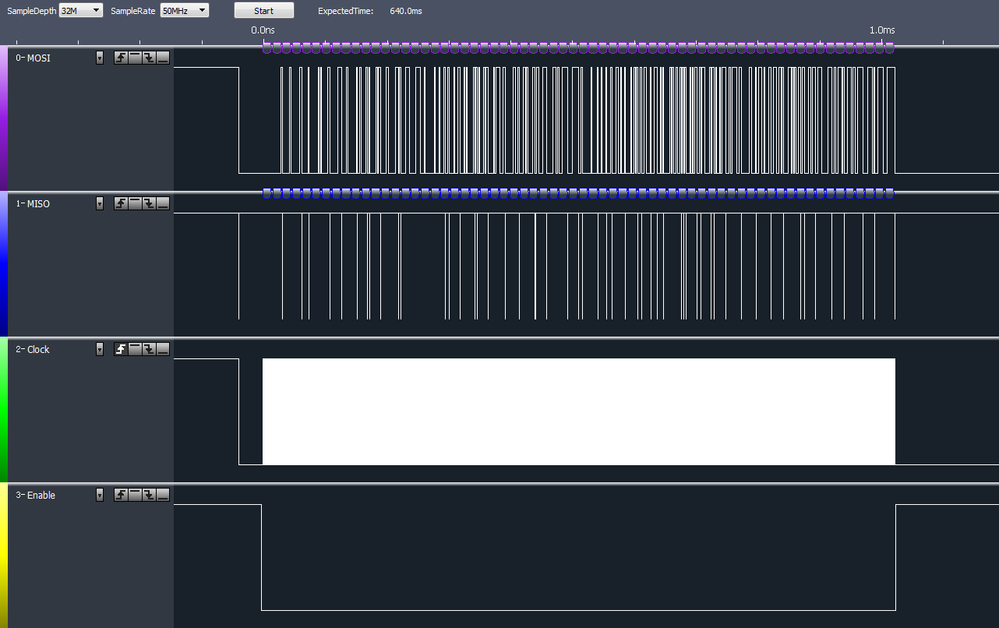

The SPI wave is tested as this:

The CS will be de-asserted after the last byte is sent by the interrupt.

More details, you can check SPI_MASTER_IRQHandler in spi_interrup_b2c_master.c.

Wish it helps you.

If you still have question about it, please kindly let me know.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kerry

Thank you for your answer.

I think,

In SPI_MASTER_IRQHandler (spi\interrupt_b2b\master ), Every receiving 1 byte, interrupt occurs.

I want long interval of interrupt.

I found the sample named ."interrupt_b2b_transfer/master"

In this interrupt is SPI_MasterTransferHandleIRQ.

I think fifo for interrupt exists.

And intterupt occurs when fifo is full.

Is it correct?

In SPI_MasterTransferHandleIRQ,When last data recieved,interrupt calls Mastercallback.

In Mastercallback,masterFinished is set.

Is it correct?

Why masterFinished is set in Mastercallback?

I think ,it's no problem even if masterFinished is set in MasterTransferHandleIRQ.

Is it correct?

makoto okuyama

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi makoto,

If you check the SPI_MasterTransferHandleIRQ, you will find the Mastercallback is called just in SPI_MasterTransferHandleIRQ:

void SPI_MasterTransferHandleIRQ(SPI_Type *base, spi_master_handle_t *handle)

{

assert((NULL != base) && (NULL != handle));

/* IRQ behaviour:

* - first interrupt is triggered by empty txFIFO. The transfer function

* then tries empty rxFIFO and fill txFIFO interleaved that results to

* strategy to process as many items as possible.

* - the next IRQs can be:

* rxIRQ from nonempty rxFIFO which requires to empty rxFIFO.

* txIRQ from empty txFIFO which requires to refill txFIFO.

* - last interrupt is triggered by empty txFIFO. The last state is

* known by empty rxBuffer and txBuffer. If there is nothing to receive

* or send - both operations have been finished and interrupts can be

* disabled.

*/

/* Data to send or read or expected to receive */

if ((handle->txRemainingBytes) || (handle->rxRemainingBytes) || (handle->toReceiveCount))

{

/* Transmit or receive data */

SPI_TransferHandleIRQInternal(base, handle);

/* No data to send or read or receive. Transfer ends. Set txTrigger to 0 level and

* enable txIRQ to confirm when txFIFO becomes empty */

if ((!handle->txRemainingBytes) && (!handle->rxRemainingBytes) && (!handle->toReceiveCount))

{

base->FIFOTRIG = base->FIFOTRIG & (~SPI_FIFOTRIG_TXLVL_MASK);

base->FIFOINTENSET |= SPI_FIFOINTENSET_TXLVL_MASK;

}

else

{

uint32_t rxRemainingCount = SPI_BYTES_TO_COUNT(handle->dataWidth, handle->rxRemainingBytes);

/* If, there are no data to send or rxFIFO is already filled with necessary number of dummy data,

* disable txIRQ. From this point only rxIRQ is used to receive data without any transmission */

if ((!handle->txRemainingBytes) && (rxRemainingCount <= handle->toReceiveCount))

{

base->FIFOINTENCLR = SPI_FIFOINTENCLR_TXLVL_MASK;

}

/* Nothing to receive or transmit, but we still have pending data which are bellow rxLevel.

* Cannot clear rxFIFO, txFIFO might be still active */

if (rxRemainingCount == 0)

{

if ((handle->txRemainingBytes == 0) && (handle->toReceiveCount != 0) &&

(handle->toReceiveCount < SPI_FIFOTRIG_RXLVL_GET(base) + 1))

{

base->FIFOTRIG =

(base->FIFOTRIG & (~SPI_FIFOTRIG_RXLVL_MASK)) | SPI_FIFOTRIG_RXLVL(handle->toReceiveCount - 1);

}

}

/* Expected to receive less data than rxLevel value, we have to update rxLevel */

else

{

if (rxRemainingCount < (SPI_FIFOTRIG_RXLVL_GET(base) + 1))

{

base->FIFOTRIG =

(base->FIFOTRIG & (~SPI_FIFOTRIG_RXLVL_MASK)) | SPI_FIFOTRIG_RXLVL(rxRemainingCount - 1);

}

}

}

}

else

{

/* Empty txFIFO is confirmed. Disable IRQs and restore triggers values */

base->FIFOINTENCLR = SPI_FIFOINTENCLR_RXLVL_MASK | SPI_FIFOINTENCLR_TXLVL_MASK;

base->FIFOTRIG = (base->FIFOTRIG & (~(SPI_FIFOTRIG_RXLVL_MASK | SPI_FIFOTRIG_RXLVL_MASK))) |

SPI_FIFOTRIG_RXLVL(handle->rxWatermark) | SPI_FIFOTRIG_TXLVL(handle->txWatermark);

/* set idle state and call user callback */

handle->state = kStatus_SPI_Idle;

if (handle->callback)

{

(handle->callback)(base, handle, handle->state, handle->userData);

}

}

}

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------