- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Why does I2C Expander send NAK when master writes a byte?

Why does I2C Expander send NAK when master writes a byte?

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why does I2C Expander send NAK when master writes a byte?

09-06-2019

07:34 AM

9,728 Views

anaseem

Contributor IV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

NXP LPC11E68JBD48E Microcontroller I2C1 is Master. I2C1 is in chapter 13. I2C1 is in Master Transmitter Mode.

http://www.mouser.com/ds/2/302/UM10732-315822.pdf

http://www.mouser.com/ds/2/302/UM10732-315822.pdf

NXP PCAL6416A I2C 16-bit I/O Expander is Slave. https://www.nxp.com/docs/en/data-sheet/PCAL6416A.pdf

I2C1 Block in Microcontroller is initialized successfully.

Step 1. I2C1 block is in master transmitter mode because I2C control Register STA bit is set to 1. See attached step1_Master_Transmitter_Mode.png file.

Step 2. Microcontroller I2C1 block transmits START bit. After the START bit is transmitted, the Serial Interrupt(SI) bit in I2C Control Register is set and STAT register in microcontroller I2C1 block contains status of 0x08. See attached filename step2_start_bit_sent.png

step 3. The status 0x08 is used to vector to a state service routine. This routine loads the slave address and Write bit to the DAT register. See attached filename step3_status_0x08_state_handler.png

step 4. Slave address and Write bit has been transmitted and negative acknowledgement(NAK) is received from slave. The STAT register has status of 0x20 and microcontroller fires interrupt on this status value. See attached step4a_NAK_from_slave.png file and step4b_NAK_handler.png

This problem occurs the very first time Master tries to communicate with slave.

The previous hardware works fine with this microcontroller and NXP PCA6408AHKX I2C 8-bit Expander chip. When this byte is written to I2C register, ACK is received.

New hardware is same as previous hardware except 16-bit I/O expander instead of 8-bit.

What might be the problem? Is it hardware or software? What are usually reasons for NAK in I2C communication?

Reply

4 Replies

09-06-2019

09:39 AM

9,581 Views

anaseem

Contributor IV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The byte I'm sending is 0x42. Seven most significant bits are slave address and least significant bit is write direction bit. Please see attached filename byte_sent.png

09-10-2019

01:20 PM

9,581 Views

anaseem

Contributor IV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

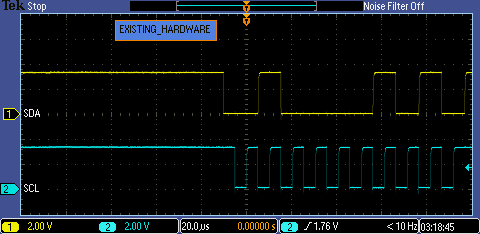

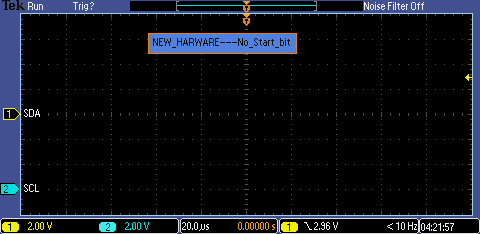

Attached are scope screenshots for existing hardware and new hardware.

With existing hardware, slave sends an ACK.

With new hardware, after START condition is transmitted, master fires an interrupt to inform software that START bit has been transmitted but I don't see it on SDA line. I'm triggering on START bit. What might be the problem?

Some inputs in the I2C expander chip are floating. Is this preventing the START bit to appear on the SDA line?

From I2C expander datasheet: "External resistors are required for inputs (on P Port) that may float. Also, internal pull-up or pull-down may be used to eliminate the need for external components."

Some inputs in the I2C expander chip are floating. Is this preventing the START bit to appear on the SDA line?

From I2C expander datasheet: "External resistors are required for inputs (on P Port) that may float. Also, internal pull-up or pull-down may be used to eliminate the need for external components."

09-11-2019

08:04 PM

9,580 Views

NXP TechSupport

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Amer,

Please check the datasheet of I2C Expander, whether send the right data to it.

Also you can attach your project, we will help to check the code.

BR

Alice

Reply

09-13-2019

05:44 AM

9,580 Views

anaseem

Contributor IV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem Solved:

First new board: saw NAK in software

Second new board: SCL and SDA no wiggling at all

Third and Fourth Board: I2C communication working as expected