- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- The problem for dual SPI output

The problem for dual SPI output

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

The problem for dual SPI output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

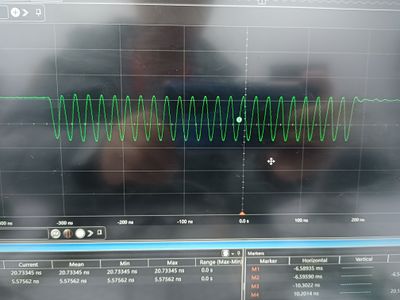

I use FC9 SPI as the master device. Send 24 clocks by writing three 8-bit data to the FIFO. The picture below is the clock waveform when sending.

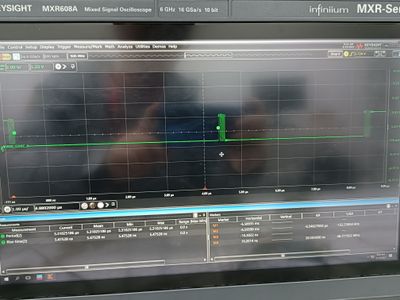

But when I utilize both FC9 SPI and FC3 SPI in the same way, there is a long time gap between 3 8-bit data transmissions.

Below is part of my code

while (1)

{

if((SPI_GetStatusFlags(EXAMPLE_SPI_MASTER) & kSPI_TxEmptyFlag)&&VCC_discharge_flag)

{

EXAMPLE_SPI_MASTER->FIFOWR = 0x74e0008;

EXAMPLE_SPI_MASTER->FIFOWR = m | 0x74e0000;

EXAMPLE_SPI_MASTER->FIFOWR = 0x75e00FC;

m = m + 11;

}

if(m > 0xEE)

{

VCC_discharge_flag=0;

}

if((SPI_GetStatusFlags(EXAMPLE_SPI_MASTER_VCCQ) & kSPI_TxEmptyFlag)&&VCCQ_discharge_flag)

{

EXAMPLE_SPI_MASTER_VCCQ->FIFOWR = 0x7470008;

EXAMPLE_SPI_MASTER_VCCQ->FIFOWR = n | 0x7470000;

EXAMPLE_SPI_MASTER_VCCQ->FIFOWR = 0x75700FC;

n = n + 11;

}

if(n > 0xEE)

{

VCCQ_discharge_flag=0;

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Tang

I have read your code, the control part of the FIFOWR register are 0x0x074E, 0x074E and 0x075E, the EOF(End of Frame) bit is NOT set, delay time is not inserted, I think the control code are correct.

From the spi clock signal waveform on the scope, it appears that the square-waveform clock signal becomes a sine signal, I suppose the SPI clock signal(SCK) frequency is too high, which highlights the gap between two bytes.

Pls try to reduce the spi clock frequency.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I hope someone can help me!!!!!!!!Thanks