- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: TDM Mode 0 Interfacing using Qualifier...

TDM Mode 0 Interfacing using Qualifier...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TDM Mode 0 Interfacing using Qualifier...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good Day,

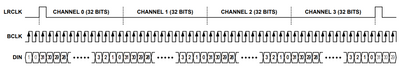

We plan to implement a TDM Mode 0 between (2) LPC4300.

One will act as a Master and the other will act as a slave transmitting and receiving 32bit data.

We are facing an issue of missing out the bit 31 is always missed out upon the Falling edge of FSYNC pin. We are planning to use the qualifier to sync the 32bit-DATAIN and FSYNC. And is it possible to have the FSYNC Data to trigger the qualifier on Rising Edge instead of Falling Edge?

Thanks and Good Day,

Leo Pestanas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In general, for I2S module, the DATAIN and FSYNC and SCK must be synchronized or from the same source, can you give more detailed information for the signal relationship among DATAIN and FSYNC and SCK signals

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XiangJun,

For example, the SGPIO Configuration intended were as follows in TX Mode 0:

- SGPIO8 - LRCLK

- SGPIO9 - BCLK

- SGPIO10 - DATAIN

- SGPIO6 - DATAOUT

If we were to use the qualifier enabled for LRCLK, are we able to frame the 32bit data without shifting by one bit? We would like to seek assistance on what would be the related registers to be initialized to achieve the syncing of LRCLK using the qualifier? And the clock source to be used is coming from PLL0Audio. We are not concerned about data justification (left/right). We just want a plain random binary data that will not shift by one bit.

Thanks and Good Day,

Leo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding your question, I am not very clear.

I suppose that you can get the SGPIO8 - LRCLK signal by shifting 4 words(32 bits each word), but only the MSB of first word is 1, all the other bits in 4 words are 0, is it okay?

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XiangJun,

Yes, for example the channel data size is 32bits and start and end has an LRCLK Pulse invoked to mark the start and end of the transmission. For example, the data is 0010 0000 0000 0000 and to be transmitted. The receiving side sees 0001 0000 0000 0000 using Mode 0 TDM. What we are planning now is to make the LRCLK to be a GPIO instead of SGPIO to make the LRCLK more faster.

Thanks,

Leo