- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- SSP1 Clock on LPC18xx is continuous

SSP1 Clock on LPC18xx is continuous

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am working to interface uSD card using SSP1 controller of LPC1837 (In built SD controller is fixed for some other functionality).

SSP1 controller is configured in master SPI mode with CPOL & CPOH as 0. I have seen the clock is coming continuously just after initialising the SSP1 module without even starting the actual transfer of the data. This is not expected behaviour, please give your inputs If I am missing anything during configuration.

Thanks.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am seeing the same behavior on our LPC1857. The main issue is that in production, the SDcards become useless.

We need a fix for this as the customers complain.

Kind regards,

Ionut Alexa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am seeing the same behavior on our LPC1857. The main issue is that in production, the SDcards become useless.

We need a fix for this as the customers complain.

Kind regards,

Ionut Alexa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi lonut Alexa,

Thanks for your response in clarifying.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Carlos Mendoza,

Thanks for your response.

Following my setup details

- LPCXpress IDE

- lpcopen_3_01_lpcxpresso_nxp_lpcxpresso_1837 example source

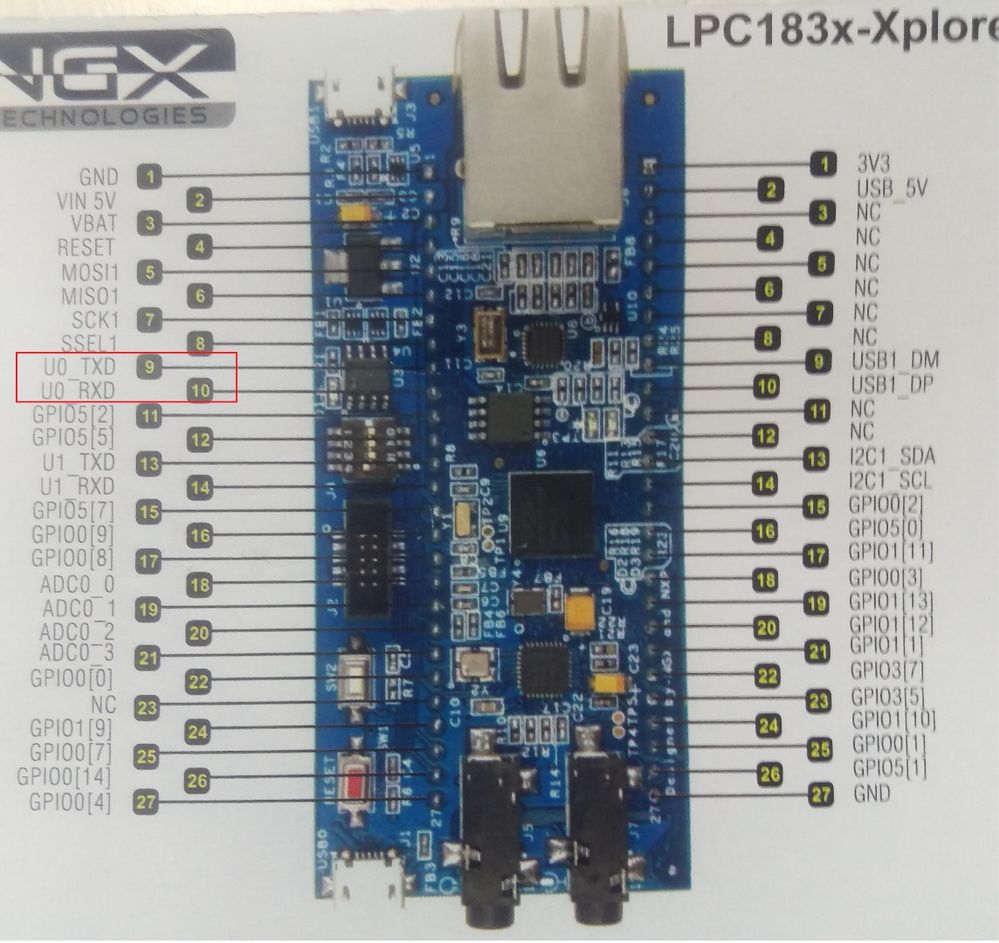

- IKALogic analyzer capture CLK, MISO, MOIS @1Mz (also used 5 & 10MHz sampling), Signals probed are shown below

- Working on LPC183x-Xplorer board.

I have shorted MISO line to MOSI line that is pin 5, 6 of J8 are shorted.

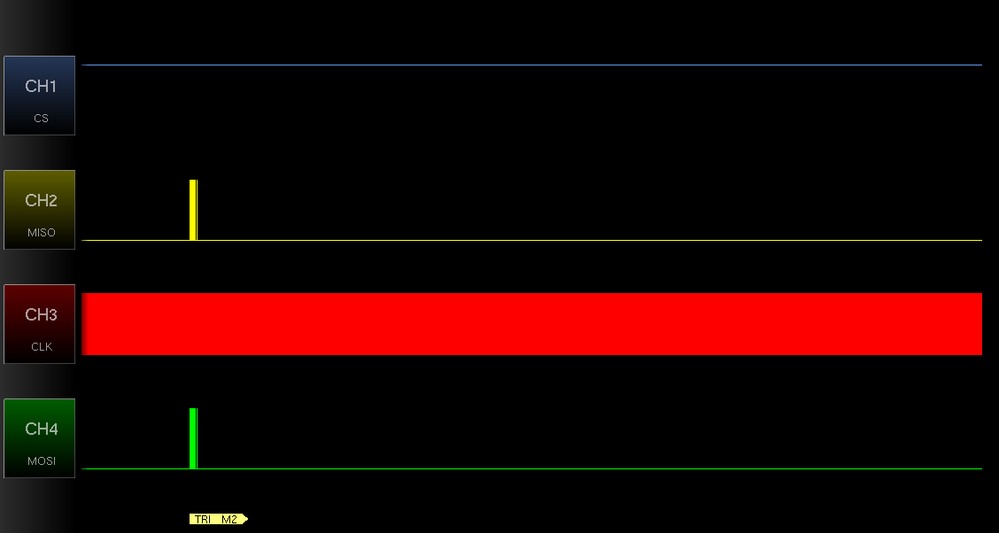

I have probed signal on logic change of the clock line, I see peculiar behavior of clock, Please give your comments

CLK is red line

Following is the serial console output, it shows transfer is passed as the MOSI & MISO are proper, but clock is not as expected/

Please give your comments why I am seeing the clock with 50% duty cycle?

I see clock is coming even though there is no data transmission. In the below scenario I have transmitted 6bytes, but the clock is keep on ticking??

Please give your inputs.

Thanks & Regards,

Vamshi G.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vamshi,

I would recommend you to compare your configuration with the one from the periph_ssp example from th eLPCOpen package, the example describes how to use SSP in POLLING, INTERRUPT or DMA mode:

LPCOpen Software for LPC18XX|NXP

Hope it helps!

Best Regards,

Carlos Mendoza

Technical Support Engineer