- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: SDRAM Configuration

SDRAM Configuration

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SDRAM Configuration

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am using MT48LC8M32B2 -7 IT (256Mbit, 8Mx16, 4 Banks, Row=12, Column=9) SDRAM on my LPC4357 board.

When i try to store 32bit data in RAM, it saves the different value sometimes.

I stored 10, but i saw 655360 in debug.

However the same program runs well on my LPC4357 Dev Board. It has MT48LC8M32B2 -6 (256Mbit, 8Mx16, 4 Banks, Row=12, Column=9) SDRAM. Only difference of SDRAM configuration between two boards is

[color=#36f]Dev Board:[/color]

Quote:

LPC_EMC->DYNAMICCONFIG0 = 1<<14| 1<<12| 2<<9 | 1<<7; /* 256Mb, 8Mx16, 4 banks, row=12, column=9 */

*((volatile uint32_t *)(SDRAM_ADDR_BASE | (0x32)<<(11))); /* 4 burst, 3 CAS latency */

[color=#36f]My Board:[/color] (Same as CMSIS Driver)

Quote:

LPC_EMC->DYNAMICCONFIG0 = 0<<14 | 1<<9 | 1<<7; /* 64Mb, 4Mx16, 4 banks, row=12, column=8 */

*((volatile uint32_t *)(SDRAM_ADDR_BASE | (3<<4 | 3)<<11)); /* 8 burst, 3 CAS latency*/

I have tried Dev Board's configuration but LCD is not running well.

Other hardware difference is

SDRAM Timing (Cycle Time) :

MT48LC8M32B2 -6 : 6ns (166 MHz)

MT48LC8M32B2 -7 : 7ns (143 MHz)

I need help to configure SDRAM.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

hope you are still around.

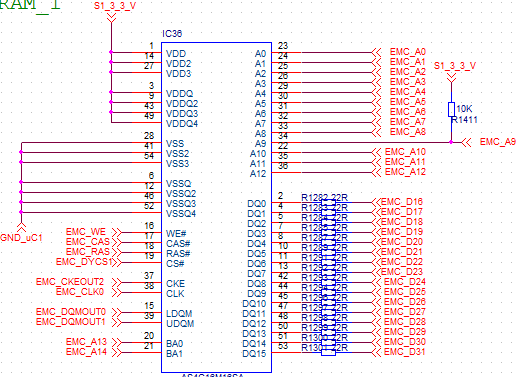

I am trying to connect the AS4C16M16SA SDRAM (256Mbit, 16Mx16, 4 Banks, Row=12, Column=9) with my LPC4370, over the EMC interface.

My Configuration is nearly the same as the one you are using, so I am pretty sure the software is correct. Nevertheless it is not possible to write data in or out of the device. Thats why I assume that the hardware is incorrectly.

My problem is that I am not sure if it is possible to use the SDRAM in the way I connected it. Could you maybe take a look over my schematic and tell me if it is possible to connect the device this way?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sven,

I don't know the specific device (CPU) you are using, but most I have seen needs to use the correct CKEx signal with regards to the DYCSx (if using DYCS1, you will need to use CKE1 also). I always use f.ex DYCS0, CKE0 and CLK0 etc

If that is the case with the CPU you are using I don't know, but maybe worth checking...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks. :D

Development board SDRAM is configured with 4 bursts.

I have tried Dev Board's configuration on my board but it did not work.

However problem is solved by using EMCDELAYCLK.

LPC_SCU->EMCDELAYCLK = 0x5555;

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

adityapadaria, if you're still around... would you mind sharing your SDRAM init code with me (here or through PM)? I use the same SDRAM chip and MCU and see some weird issues, so it would be extremely helpful to compare the init sequence and timing parameters.

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

/******************************************************************************************/

/******************************************************************************************/

#include "lpc43xx.h"

#include "lpc43xx_scu.h"

/******************************************************************************************/

/******************************************************************************************/

#define SDRAM_ADDR_BASE 0x28000000 // SDRAM Address Base for DYCS0

/******************************************************************************************/

/******************************************************************************************/ // SDRAM_Init

void SDRAM_Init(void)

{

/******************************************************************************************/

uint32_t i;

/******************************************************************************************/ // Set up EMC pins

// EMC Address pins

scu_pinmux(0x2, 9, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A0

scu_pinmux(0x2, 10, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A1

scu_pinmux(0x2, 11, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A2

scu_pinmux(0x2, 12, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A3

scu_pinmux(0x2, 13, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A4

scu_pinmux(0x1, 0, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A5

scu_pinmux(0x1, 1, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A6

scu_pinmux(0x1, 2, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A7

scu_pinmux(0x2, 8, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A8

scu_pinmux(0x2, 7, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); //A9

scu_pinmux(0x2, 6, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A10

scu_pinmux(0x2, 2, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A11

scu_pinmux(0x2, 1, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A12

scu_pinmux(0x2, 0, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); //A13

scu_pinmux(0x6, 8, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC1); //A14

// EMC Data pins

scu_pinmux(0x1, 7, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_7: D0 (function 0) errata */

scu_pinmux(0x1, 8, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_8: D1 (function 0) errata */

scu_pinmux(0x1, 9, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_9: D2 (function 0) errata */

scu_pinmux(0x1, 10, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_10: D3 (function 0) errata */

scu_pinmux(0x1, 11, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_11: D4 (function 0) errata */

scu_pinmux(0x1, 12, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_12: D5 (function 0) errata */

scu_pinmux(0x1, 13, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_13: D6 (function 0) errata */

scu_pinmux(0x1, 14, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* P1_14: D7 (function 0) errata */

scu_pinmux(0x5, 4, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_4: D8 (function 0) errata */

scu_pinmux(0x5, 5, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_5: D9 (function 0) errata */

scu_pinmux(0x5, 6, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_6: D10 (function 0) errata */

scu_pinmux(0x5, 7, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_7: D11 (function 0) errata */

scu_pinmux(0x5, 0, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_0: D12 (function 0) errata */

scu_pinmux(0x5, 1, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_1: D13 (function 0) errata */

scu_pinmux(0x5, 2, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_2: D14 (function 0) errata */

scu_pinmux(0x5, 3, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* P5_3: D15 (function 0) errata */

scu_pinmux(0xD, 2, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_2: D16 (function 0) errata */

scu_pinmux(0xD, 3, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_3: D17 (function 0) errata */

scu_pinmux(0xD, 4, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_4: D18 (function 0) errata */

scu_pinmux(0xD, 5, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_5: D19 (function 0) errata */

scu_pinmux(0xD, 6, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_6: D20 (function 0) errata */

scu_pinmux(0xD, 7, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_7: D21 (function 0) errata */

scu_pinmux(0xD, 8, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_8: D22 (function 0) errata */

scu_pinmux(0xD, 9, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2); /* PD_9: D23 (function 0) errata */

scu_pinmux(0xE, 5, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_5: D24 (function 0) errata */

scu_pinmux(0xE, 6, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_6: D25 (function 0) errata */

scu_pinmux(0xE, 7, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_7: D26 (function 0) errata */

scu_pinmux(0xE, 8, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_8: D27 (function 0) errata */

scu_pinmux(0xE, 9, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_9: D28 (function 0) errata */

scu_pinmux(0xE, 10, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_10: D29 (function 0) errata */

scu_pinmux(0xE, 11, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_11: D30 (function 0) errata */

scu_pinmux(0xE, 12, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3); /* PE_12: D31 (function 0) errata */

// EMC control pins

scu_pinmux(0x6, 12, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //DQMOUT0

scu_pinmux(0x6, 10, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //DQMOUT1

scu_pinmux(0xD, 0, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC2 ); //DQMOUT2

scu_pinmux(0xE, 13, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //DQMOUT3

scu_pinmux(0x6, 9, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //DYCS0

scu_pinmux(0x1, 6, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //WE

scu_pinmux(0x6, 5, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //RAS

scu_pinmux(0x6, 4, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //CAS

scu_pinmux(0x6, 11, (MD_PLN | MD_EZI | MD_ZI | MD_EHS), FUNC3 ); //CKEOUT0

/******************************************************************************************/ // Select EMC clock-out

LPC_SCU->SFSCLK_0 = MD_PLN_FAST;

LPC_SCU->SFSCLK_1 = MD_PLN_FAST;

LPC_SCU->SFSCLK_2 = MD_PLN_FAST;

LPC_SCU->SFSCLK_3 = MD_PLN_FAST;

/******************************************************************************************/

LPC_SCU->EMCDELAYCLK = 0x5555;

/******************************************************************************************/

LPC_EMC->CONTROL = 0x00000001;

LPC_EMC->CONFIG = 0x00000000;

/******************************************************************************************/

// /* RBC (Row, Bank, Column) : 32 bit external bus high-performance address mapping */

// /* 256 Mbit, 8Mx32, 4 Banks, 12 Row, 9 Column */

// LPC_EMC->DYNAMICCONFIG0 = 1<<14| 2<<9 | 1<<7;

/* BRC (Bank, Row, Column) : 32 bit external bus address mapping */

/* 256 Mbit, 8Mx32, 4 Banks, 12 Row, 9 Column */

LPC_EMC->DYNAMICCONFIG0 = 1<<14| 1<<12| 2<<9 | 1<<7;

/******************************************************************************************/

LPC_EMC->DYNAMICRASCAS0 = 0x00000303; /* 3 CAS, 3 RAS latency */

LPC_EMC->DYNAMICREADCONFIG = 0x00000001; /* Command delayed strategy, using EMCCLKDELAY */

LPC_EMC->DYNAMICRP = 2;

LPC_EMC->DYNAMICRAS = 5;

LPC_EMC->DYNAMICSREX = 8;

LPC_EMC->DYNAMICAPR = 1;

LPC_EMC->DYNAMICDAL = 5;

LPC_EMC->DYNAMICWR = 1;

LPC_EMC->DYNAMICRC = 8;

LPC_EMC->DYNAMICRFC = 8;

LPC_EMC->DYNAMICXSR = 8;

LPC_EMC->DYNAMICRRD = 1;

LPC_EMC->DYNAMICMRD = 1;

/******************************************************************************************/

for(i = 0; i < 1000; i++); /* wait 128 AHB clock cycles */

LPC_EMC->DYNAMICCONTROL = 0x00000183; /* Issue NOP command */

for(i = 0; i < 1000; i++); /* wait 128 AHB clock cycles */

/******************************************************************************************/

LPC_EMC->DYNAMICCONTROL = 0x00000103; /* Issue PALL command */

LPC_EMC->DYNAMICREFRESH = 2;

for(i = 0; i < 1000; i++); /* wait 128 AHB clock cycles */

LPC_EMC->DYNAMICREFRESH = 110;

/******************************************************************************************/

LPC_EMC->DYNAMICCONTROL = 0x00000083; /* Issue MODE command */

/* Timing for 48/60/72MHZ Bus */

// /* RBC (Row, Bank, Column) : 32 bit external bus high-performance address mapping */

// *((volatile uint32_t *)(SDRAM_ADDR_BASE | (3<<4 | 2)<<13)); /* 4 Burst, 3 CAS latency, 13 for RBC */

/* BRC (Bank, Row, Column) : 32 bit external bus address mapping */

*((volatile uint32_t *)(SDRAM_ADDR_BASE | (3<<4 | 2)<<11)); /* 4 Burst, 3 CAS latency, 11 for BRC */

/******************************************************************************************/

LPC_EMC->DYNAMICCONTROL = 0x00000000; /* Issue NORMAL command */

/******************************************************************************************/

LPC_EMC->DYNAMICCONFIG0 |= 1<<19; /* [re]enable buffers */

/******************************************************************************************/

}

/******************************************************************************************/

/******************************************************************************************/

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Great, thank you very much!

Do you also use the MCU clock running at 204 MHz and the EMC clock with the divider at 102 MHz like this?

LPC_CCU1->CLKCCU[CLK_MX_EMC_DIV].CFG |= (1 << 5);

LPC_CREG->CREG6 |= (1 << 16);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

A 32-bit wide SDRAM has to be configured with 4 bursts, a 16-bit wide SDRAM with 8 bursts.

The background is, that the SDRAM controller in the LPC1800/LPC4300 always fetches 16 bytes from the SDRAM, even when only one byte is requested.

This means that with a 32-bit bus the SDRAM controller fetches 4 times 32 bits to achieve 16 bytes, for a 16-bit bus it is 8 times. This is meant with burst size 4 and burst size 8.

Regards,

NXP Support Team