- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: READ OPERATION - LPC55S36 IN TARGET MODE

READ OPERATION - LPC55S36 IN TARGET MODE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

READ OPERATION - LPC55S36 IN TARGET MODE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi! I have an issue that I hope you can help me solve.

We are trying to implement the read operation in the target mode using the LPC55S36. With this purpose we use another LPC55S36 in controller mode which inits the bus (handles the DAA), writes to the target an array of 6 bytes, and then reads 6 bytes from it. The idea to test the correct target read operation is to see (using the Logic Saleae sniffer) the same data written (read by the controller) than the one previously read (written by the controller) using a shared buffer to handle the data from both transactions.

So far, we haven´t had any problems regarding using different CCCs like RSTDAA, SETDASA, ENTDAA, SETMRL, GETMRL. They return the data we´ve previously set during the initialization in the respective registers (if that is the case) and we can see the right operation using the sniffer.

With the write operation (controller reads) we saw no problem either. If we specify an array in the code during the target initialization, and then write it into the bus using I3C_SINTMASKED_TXSEND_MASK interrupt and SWDATAB and SWDATABE registers, we see the right bytes on the bus using the sniffer.

Now, the problem with the target read operation is that, although we see the controller write operation in the sniffer (started and finished correctly with the right data), the data doesn´t seem to be saved correctly on a the array. When, in the next operation the controller reads the data from the target, the data that was initially set during intitialization is the one returned, not the one actually written by the controller.

Taking into account that the write operation (controller reads) alone works fine, we conclude it is the read operation (controller writes) that has a problem.

I have not seen much explanation in the datasheet about the interrupts triggered during target mode operations, as there are when working in controller mode. I´ve taken the SDK example as a reference, trying to replicate the initialization as they do there. The main difference I have is that my driver callback checks the SINTMASKED register instead of the SSTATUS one, but I don´t think that makes any difference. Is the I3C_SINTMASKED_MATCHED_MASK triggered during the read or write transactions, and is there a way of knowing before the actual transaction what it is (read or write)?

Both read and write transfers use a push pull frequency of 5 MHz and an open drain frequency of 1,25 MHz.

I´m going to attach some captures of the initialization and the read and write transfers, and a simplified version of my code.

Hope you can help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

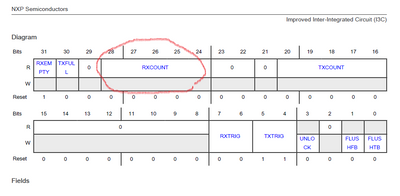

I have checked your code, you said that the I3C controller read wrong data from target, can you check the RXCOUNT bits in SDATACTRL register to know the number of the bytes the target has received, then read them by target.

BR

XiangJun Rong