- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi.I've have an issue that a port pin 0.19 on the LPC824 is set to output, it will not respond to instruction to set HIGH or LOW.

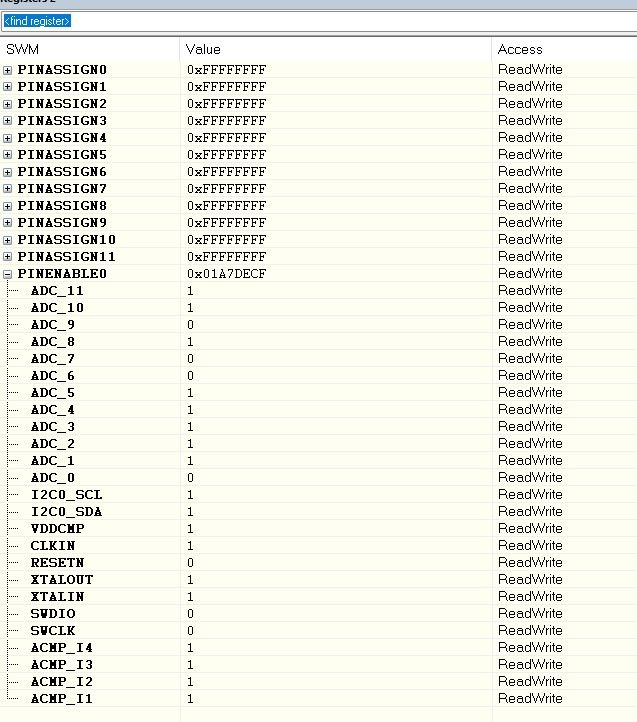

It seems that on POR, that the PINABLE0 register is clearing (which ENABLES) ADC_0, ADC_6, ADC_7 and ADC_9. Other ADC bits are set to 1, which DISABLES the ADC link to the port pin. Data sheet states that the reset state should be 1 for all ADC port pins.

I have tried this on an LPCXpresso824-MAX eval board.

I'm using IAR EWARM, which if you start from the debug enviroment it works OK, but if you start the debug code without IAR, it goes wrong.

I've started the the expresso board without IAR, it goes wrong, used the IAR connect to running target, inspected the PINENABLE0 register, which show the above register bits cleared.

I've tried a simple code example which does the same. A fix is to put a few lines of code to set those bits to 1, but they shouldn't be 0 in the first place? So that extra code shouldn't be required.

Is there something obvious I'm not doing as this would be seen by other folk, but not seen this mentioned on the forum.

Thanks

My test code

u8 test_byte;

void main(void)

{

SystemCoreClockUpdate();

//GPIO_INIT();

Chip_GPIO_Init(LPC_GPIO_PORT);

Chip_GPIO_SetPinDIR(LPC_GPIO_PORT, PORT0, 20, GPIO_OUTPUT);

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 20, HIGH);

Chip_GPIO_SetPinDIR(LPC_GPIO_PORT, PORT0, 18, GPIO_OUTPUT);

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 18, HIGH);

Chip_GPIO_SetPinDIR(LPC_GPIO_PORT, PORT0, 19, GPIO_OUTPUT);

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 19, HIGH);

// This fixes the issue !

/*

Chip_Clock_EnablePeriphClock(SYSCTL_CLOCK_SWM); // Enable the clock to the Switch Matrix

Chip_SWM_DisableFixedPin(SWM_FIXED_ADC0); //turn off ADC is on port

Chip_SWM_DisableFixedPin(SWM_FIXED_ADC6); //turn off ADC

Chip_SWM_DisableFixedPin(SWM_FIXED_ADC7); //turn off ADC

Chip_SWM_DisableFixedPin(SWM_FIXED_ADC9); //turn off ADC

Chip_Clock_DisablePeriphClock(SYSCTL_CLOCK_SWM); // Disable the clock to the Switch Matrix to save power

*/

while (1)

{

if (test_byte == 0)

{

test_byte = 1;

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 19, HIGH); // debug pulse

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 18 , HIGH);

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 20 , HIGH);

}

else

{

test_byte = 0;

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 19, LOW); // debug pulse

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 18 , LOW);

Chip_GPIO_SetPinState(LPC_GPIO_PORT, PORT0, 20 , LOW);

}

}

}

// Set up and initialize hardware prior to call to main ------------------------

void SystemInit(void)

{

SCB->VTOR = VECTORS;

}

已解决! 转到解答。

Hello, my name is Pavel, and I will be supporting our case I have some questions what is the mode you need to use GPIO or ADC? Could you elaborate further? Did you solve your issue?

Best regards,

Pavel

Hello, my name is Pavel, and I will be supporting our case I have some questions what is the mode you need to use GPIO or ADC? Could you elaborate further? Did you solve your issue?

Best regards,

Pavel

Hi Pavel.

In my actual application, I want to use Port P0.19 as a straight forward port output.

When I was testing my code the port pin wouldn't respond.

As I investigated, it seems that that pin was assigned to ADC_7.

I have not purposely assigned it to ADC_7.

I did a simple test program, as posted previously, which did the same on a LPCXpresso824-MAX board using IAR EWARM 8.11

It seems that the PINENABLE0 register is (falsely?) enabling that port pin to the ADC_7 on POR.

PINENABLE register, for bit 20 that controls ADC_7 at RESET should be SET to One. If set to One, this will DISABLE the link to ADC_7. My test’s indicate that bit is CLEARED to ZERO, which ENABLES ADC_7. Documentation for PINEABLE0 states that at reset , that bit is SET to One.

But my quick test program, when inspecting that register that bit is cleared to zero, which the documentation states it shouldn’t be? I have done this by starting the application, connecting to the running target with IAR EWARM (a great feature), halting the program and inspecting the PINENABLE0 register, as previously shown.

I have managed a “quick” work around by writing to the ENABLE0 register and setting that bit to One, BUT this should not need to be done. Why is it cleared to zero? Is there something obvious I am missing.

Problem also affects ADC_0 , 6 and 9.

I have concern that if register is not properly setting/ clearing the bits at POR, will other registers be doing wrong POR bit setting / clearing?

Grab of NXP data sheet for PINEABLE0

Screen grab of what IAR EWARM is telling me of the status of PINENABLE0

So, I have not solved my issue as I don’t understand why those bits are not correct on POR.

Thanks