- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC802 frequency Generation

LPC802 frequency Generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was using the LPC802 Controller.Where I was generate the Frequency up to 345khz When toggle the gpio pin.Is it possible to generate up to 2.4MHz.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, sorry for the late response, I was researching more information on the reference manual and datasheet.

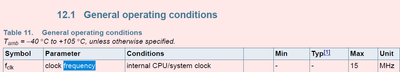

The maximum clock source is 15mhz.

The documentation of the Ctimer source is from the AHBCLKCTRL0.

The LPC802 supports a clock up to 15MHz which gives us a clock cycle period of 66ns, and the documentation regarding interrupt latency of Arm (You can look at it on this link Interrupt Latency) states that the Cortex-M0+'s clock cycles with zero wait state memory are 15.

Interrupt Time = CyclesClock * period = 15 * 66ns = 1us

After reviewing the documentation value below 1us is not possible.

Best regards,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, my name is Pavel, and I will be supporting your case, could you elaborate further about how you your questions? Did you use the Ctimer example on the SDK?

Let me research more information about the last question.

Best regards,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also In polling method, i make a code only for toggle as following main(){while(1){

GPIO->SET[0]|=(1<<17);

GPIO->CLR[0]|=(1<<17);

}}

In this also, it achieve only upto 340 KHz(nearly 2.4 us).

Kindly give the solution for this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I do not recommend using the timer at 1ns, intend of I recommend using it at a minimum of 100ns if you are using an interrupt put a counter or other solution to count 4 cycles to get 400ns.

Best regards,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to configure timer for 100 ns (using MR value of 1 and 2), but it works only upto 10 us (MR value of 120)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, sorry for the late response, I was researching more information on the reference manual and datasheet.

The maximum clock source is 15mhz.

The documentation of the Ctimer source is from the AHBCLKCTRL0.

The LPC802 supports a clock up to 15MHz which gives us a clock cycle period of 66ns, and the documentation regarding interrupt latency of Arm (You can look at it on this link Interrupt Latency) states that the Cortex-M0+'s clock cycles with zero wait state memory are 15.

Interrupt Time = CyclesClock * period = 15 * 66ns = 1us

After reviewing the documentation value below 1us is not possible.

Best regards,

Pavel