- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC55S69: enable SRAM clocks

LPC55S69: enable SRAM clocks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC55S69: enable SRAM clocks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi !

For worj with USB SRAM I should enable clock kCLOCK_UsbRam1 explictly in my code e.g. CLOCK_EnableClock(kCLOCK_UsbRam1). ConfigTool is also not generate this line in any mode.

But what about other SRAM /flash section and Flash ?

There are mentioned in clock_ip_t enumeration

kCLOCK_Sram1 = CLK_GATE_DEFINE(AHB_CLK_CTRL0, 3),

kCLOCK_Sram2 = CLK_GATE_DEFINE(AHB_CLK_CTRL0, 4),

kCLOCK_Sram3 = CLK_GATE_DEFINE(AHB_CLK_CTRL0, 5),

kCLOCK_Sram4 = CLK_GATE_DEFINE(AHB_CLK_CTRL0, 6),

kCLOCK_Flash = CLK_GATE_DEFINE(AHB_CLK_CTRL0, 7),

Are the enabled by default ? Or BootROM enable those.

Or the managed by some PowerLib API or ROM api.

How to undestand ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene!

I am working on your question.

Please, provide me additional time to check

Regards,

Diego.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene!

Thank you for your patience,

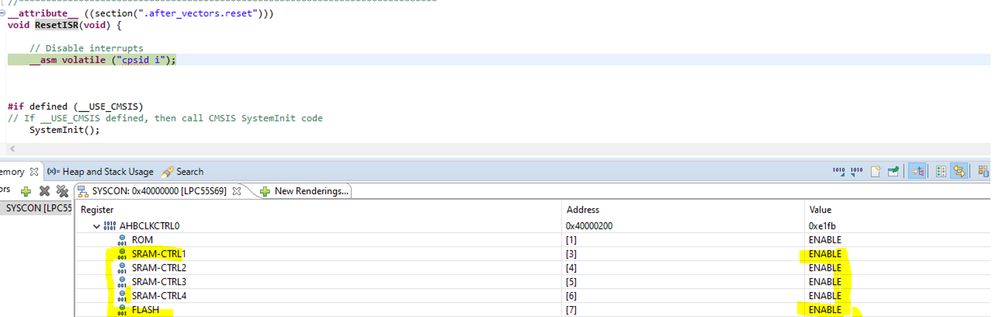

On the beginning of your application their controllers are already enabled by default, as we can see

on the following screenshot

Regards,

Diego

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi diego.charles !

I can see in UM, default value for AHBCLKCTRL0 register is specified. It means SRAMn clocks enabled somewhere in bootrom. In this case is difficult to trust if clocks always will be enabled there ( or disabled/enabled again ) and SRAM retain over reboot in next versions of bootrom if any.

By the way, I haven't found any clock enable for SRAM X area. Is this type of SRAM always ON or it is just in other registers ?

But I think it is good idea to have clear spec. in what states registers remains after bootrom.

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eugene,

You should not worry about the SRAM X areas, they are enabled by default.

As you know, you could control their retention state during low power modes using the sram_retention_ctrl register.

Regards,

Diego