- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC55S69 : Core1 and TrustZone

LPC55S69 : Core1 and TrustZone

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC55S69 : Core1 and TrustZone

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello !

It is not so clear from user/ds documents about some dependencies between some peripherals.

1. Can Core1 and their peripherals to be allocated in secure part and be fully protected from Core 0.

So Core 0 shouln't able to access to Core 1 code/data/peripherals at all ?

So like Core 1 running under Trustzone protection at secure part ?

If Core 1 generate some interrupts, Core 0 can call some secure API and read status if need ?

Looks like Core 1 should be able to access areas what is protected by Core0's Trustzone.

Or Core0 is able to exclude Core1 areas by using own MPU only ?

2. What if Core0 stay in Deepsleep mode and can Core 1 continue to to switch between Run and DeepSleep modes

and Core1 should use some GPIO lines for wakeup from DeepSleep ?

Basically I need if both Cores can switch between Run and DeepSleep freely by using own set of GPIO lines and peripherals. And able to wakeup up each other when need.

But all Core1 peripherals/memory should be at secure world.

Does this kind of configuration is possible ?

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Eugene,

Here are the answers to your questions:

1. Can Core1 and their peripherals to be allocated in secure part and be fully protected from Core 0.

So Core 0 shouln't able to access to Core 1 code/data/peripherals at all ?

So like Core 1 running under Trustzone protection at secure part ?

If Core 1 generate some interrupts, Core 0 can call some secure API and read status if need ?

The LPC55S66 and LPC55S69 have implemented core 0 as a Cortex-M33 with full TEE and TrustZone® support enabled. The LPC55S69 has a second Cortex-M33 (core 1) that does not implement the secure environment with TZ. In this case Core 0 is the secure part and Core 1 shouldn't be able to access Core 0, unless through secure gateways.

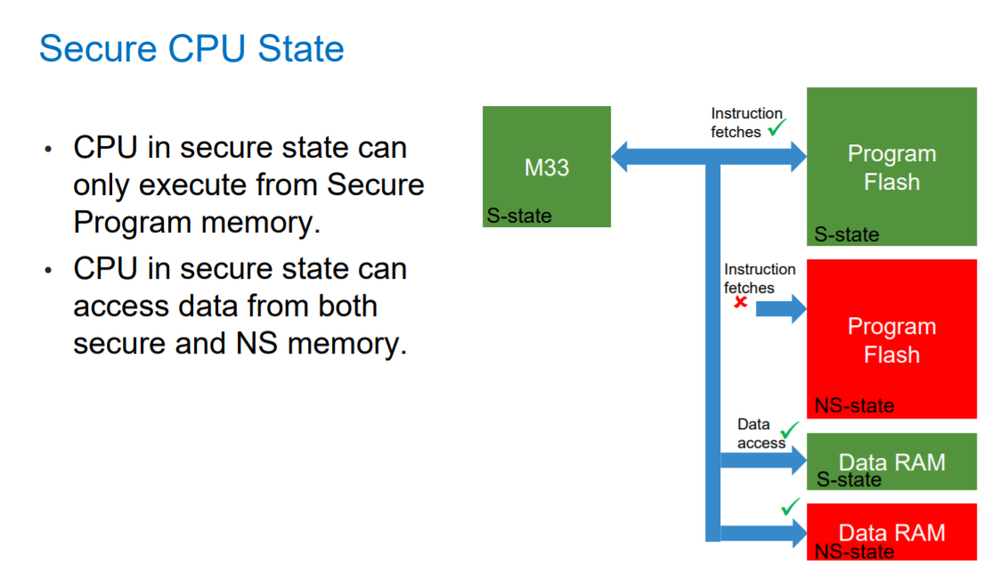

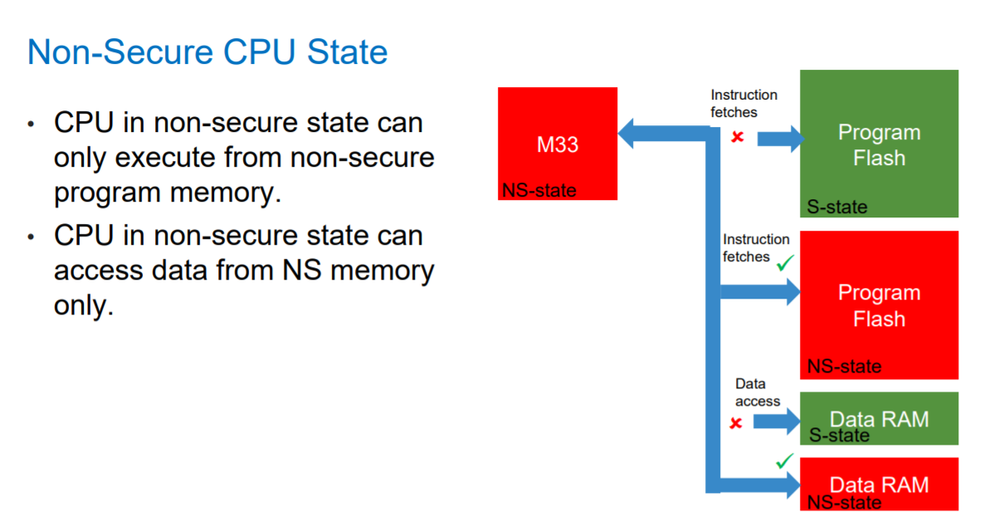

TrustZone® technology divides the system into two states, safe (S) and non-secure (NS), and can switch between the two states through corresponding commands. The CPU states can be secure privilege, secure non-privilege, privilege (Handler), or non-privilege (Thread).

What if Core0 stay in Deepsleep mode and can Core 1 continue to to switch between Run and DeepSleep modes

and Core1 should use some GPIO lines for wakeup from DeepSleep ?

Only Core 0 is able to enter deep sleep mode. core 1 is able to enter normal sleep mode. Please refere to chapter 14 for the power profiles available in the LPC55s69.You can however enter sleep mode for either CPU 0 or CPU1.

Please let me know if you have additional questions.

Best Regards,

Sabina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Sabina !

So basically Core1 can be always ON and used like this :

- it can have own Core clock and use 32kHz or 1Mhz internal oscillators as clock source and for Systick timer.

And only switch between RUN and Sleep (_ WFI()) modes.

In this case it can consume some mkA but exact digits is not visible in DS.

- Secure gateways can be configured in ways that Core1 always and Core0 in Secure mode access some part of SRAM memory.

But Core0 in Non-Secure mode can't access it.

Is this true ?

Thank you !

Regards,

Eugene

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Eugene,

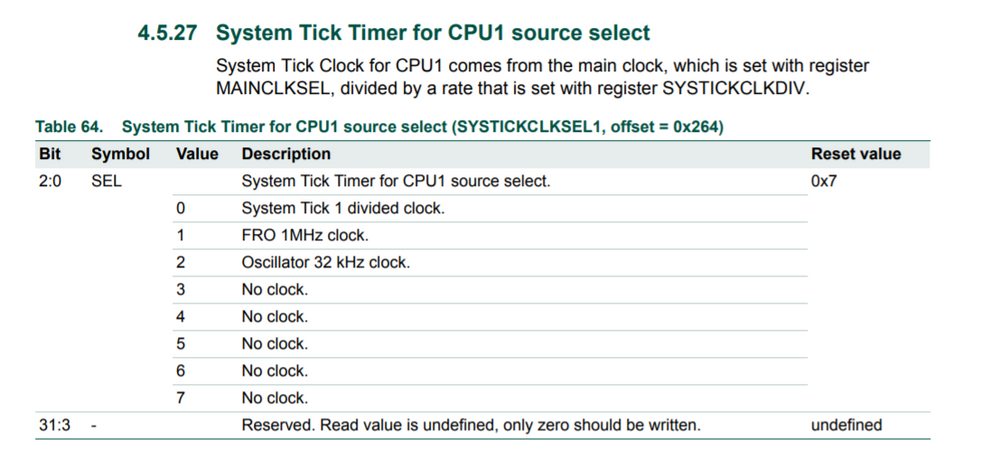

1. The System Tick timer for CPU1 has three options.

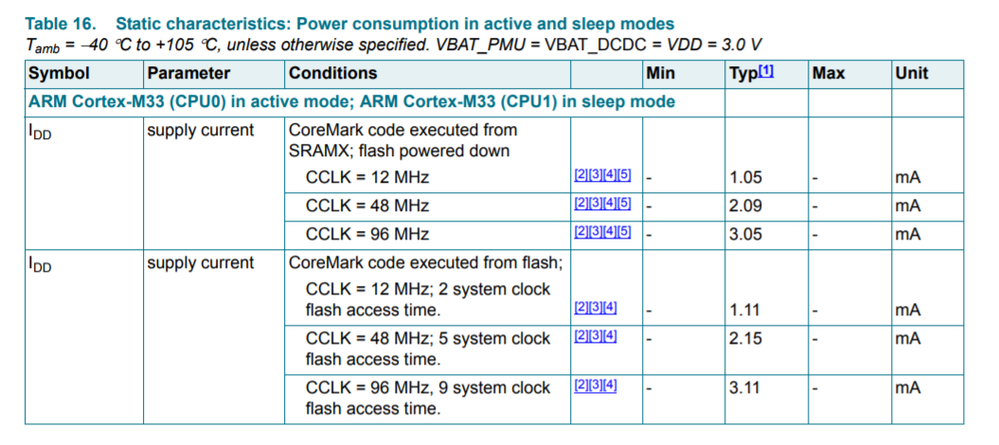

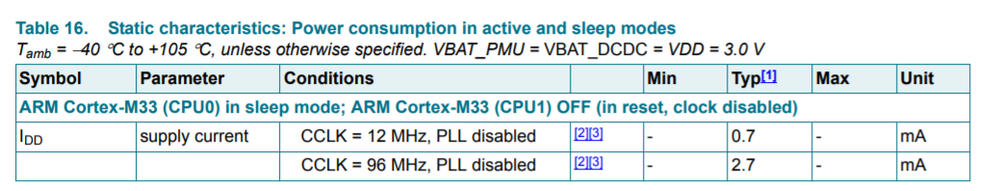

The datasheet shows the current consumption when CPU1 is in sleep mode or off.

The second question I did not understand what you mean. Here is the basic functionality if the CPU is in secure or non-secure states.

Here are some really great videos that explain in detail, how the trustzone feature works with our LPC55S6x Family.

If you have more questions let me know.

Best Regards,

Sabina