- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

I am using the SDK for the SPI0 with Flexcomm0 for the LPC54605 MCU.

I am using the SPI_MasterTransferBlocking function. It works fine, but the SPI0->STAT stalled bit is always set and the MSTIDLE flag is never set to one again. Also the SSA flag is stuck to one as well.

I need to poll for the transfer to be complete, not poll for the FIFO to be empty.

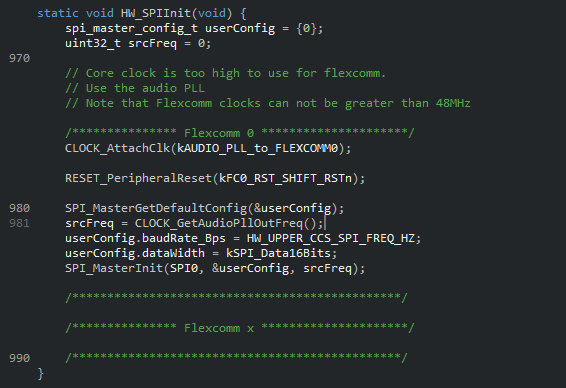

My SPI Init routine:

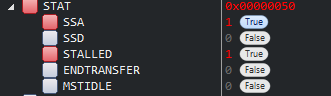

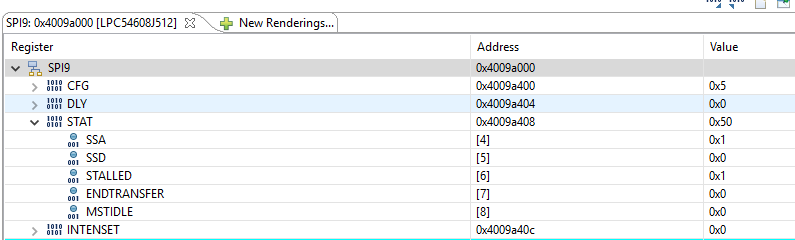

Once you start a transfer the STAT register looks like this:

And you can keep sending data just fine, but the STALLED bit stays set even when using the SPI_MasterTransferBlocking.And MSTIDLE never is set again.

I don't need to receive anything, I even set the RXIGNORE flag in FIFOWR. But that did nothing.

已解决! 转到解答。

Hi Matt Lang,

Thanks for your reply.

Q1) Does that mean a 1 needs to be written to the ENDTRANSFER by design and it's just not clear in the Reference Manual?

-- Yes.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Matt Lang,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

Whether you can tell me which exactly demo you run for testing, in further, had you done some modification about the demo?

As I'd like to replicate the phenomenon on my site for checking.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Matt Lang,

Thanks for your reply.

I've already replicated the phenomenon, I think it should add some notes in the RM to clarify or describe this phenomenon, I'll report it to RM team to further checking.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Matt Lang,

Thanks for your reply.

Q1) Does that mean a 1 needs to be written to the ENDTRANSFER by design and it's just not clear in the Reference Manual?

-- Yes.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

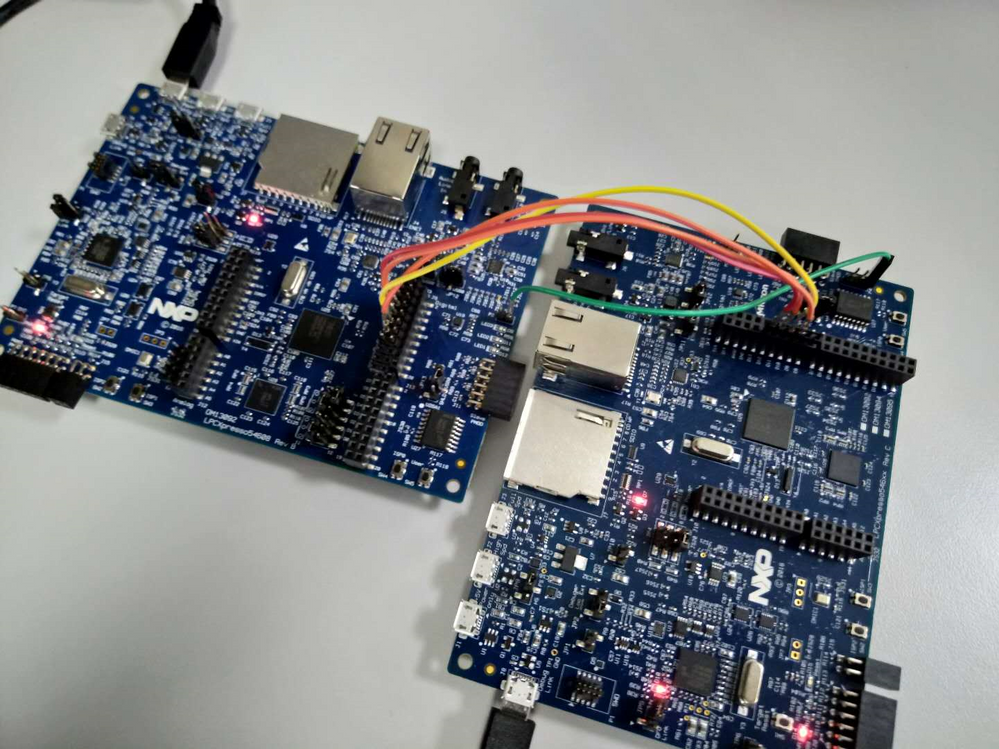

I see this with the lpcxpresso54608_driver_examples_spi_polling_b2b_transfer_master demo project with no edits.

After it calls SPI_MasterTransferBlocking(EXAMPLE_SPI_MASTER, &xfer), it is stalled and the MSTIDLE bit is never set even if you continue to step through the code.

I did this on MCUXpresso IDE this time running on the LPCXpresso654xx dev board.

In my other code, my solution was to write a 1 to the ENDTRANSFER bit in the STAT register when the last byte is send is complete. This will terminate the transfer once the current one is over and will get out of stalled and set the MSTIDLE bit. But the datasheet does not mention that this needs to be done, so i'm assuming I should not have to do this.