- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC546xx Flexcomm maximum clock frequency

LPC546xx Flexcomm maximum clock frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello-

The LPC546xx manual has this note about Flexcomm clock selection:

(Section 24.4 of UM10912 Rev 2.4)

Remark: The Flexcomm Interface function clock frequency should not be higher than

48 MHz.

We've experimented with selecting a 96MHz Audio PLL clock output for the Flexcomm interface; with a 16x oversample setting, this lets us use the maximum 6Mbaud speed for the USART (and seems to be working properly).

Is this configuration supported? Can a 96MHz clock be selected for the Flexcomm peripherals?

Thanks!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, all,

This is AE team reply:

"We need to follow UM, the maximum limit clock is 48M, this is due to design limitation."

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for looking into this. It would be really nice to have a definite reply from someone who knows the reason for the limitation, instead of "I think it can be ignored" followed by "we think it is correct". The flexcomm peripheral works fine with a 96 MHz clock from all of our testing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Anyway, I have asked the AE team what the 48MHz limitation means exactly, I will update the thread after I get reply.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, all,

This is AE team reply:

"We need to follow UM, the maximum limit clock is 48M, this is due to design limitation."

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiangjun-

Thanks for checking, much appreciated! We'll use 48MHz as the input clock to the Flexcomm.

Thanks!

Noah

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Noah,

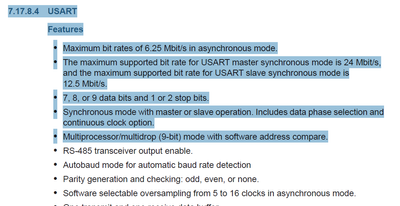

I think it is a general guide line for the Flexcomm interface, as you use USART module, pls refer to the section 7.17.8.4 USART in data sheet of LPC546xx. which can be downloaded from

As it says that the bit rate can reach up to 6.25M in asynchronous mode, the USART driving clock will be 16*6.25M=100M.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you certain that the Remark about 48 MHz can be ignored? If it is incorrect, then why is it written in the user manual?

Please note that it is possible to obtain a USART speed of 6.25M with a flexcomm clock of 48 MHz or less by setting a lower value of the OSR register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Noah,

I agree with you that reducing the oversampling from 16 bits can reduce the required uart driving clock frequency.

baud rate = [FCLK / oversample rate] / BRG divide

The BRG is USART Baud Rate Generator register,is a clock divider.

I have consulted with AE engineer, we think that the Remark about 48 MHz clock limitation is correct, you should follow up the clock limitation.

Hope it can help you

BR

Xiangjun rong