- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

LPC54102 SPI0 & SPI1 Communication issue?

Hi,

I have LPCXpresso 54102 LQFP64 Rev A (OM13077) development board & using LPCXpresso_8.1.0_597 IDE.

It is running with Cortex M4 processor at 96MHz.

I am executing the default example program "periph_spi_sm_int" to validate SPI protocol with master and slave.

I have connected spi0 & spi1 with wire in connector J3 & J1 like below

SPI0 SSEL to SPI1 SSEL

SPI0 CLK to SPI1 CLK

SPI0 MISO to SPI1 MOSI

SPI0 MOSI to SPI1 MISO

SPI communication is working with error(return error C). The below show the o/p which is received in UART terminal

SLAVE [txDoneCount = 16, rxDoneCount = 15]

MASTER [txDoneCount = 16, rxDoneCount = 16]

TRANSFER COMPLETE: errors = c

Master total transfer time = 16953uS

Showing data from : Master TX data

0x0001 0x0002 0x0003 0x0004 0x0005 0x0006 0x0007 0x0008

0x0009 0x000a 0x000b 0x000c 0x000d 0x000e 0x000f 0x0010

Showing data from : Master RX data

0xfffe 0xfffe 0xfffd 0xfffc 0xfffb 0xfffa 0xfff9 0xfff8

0xfff7 0xfff6 0xfff5 0xfff4 0xfff3 0xfff2 0xfff1 0xfff0

Showing data from : Slave TX data

0xfffe 0xfffd 0xfffc 0xfffb 0xfffa 0xfff9 0xfff8 0xfff7

0xfff6 0xfff5 0xfff4 0xfff3 0xfff2 0xfff1 0xfff0 0xffef

Showing data from : Slave RX data

0x0001 0x0003 0x0004 0x0005 0x0006 0x0007 0x0008 0x0009

0x000a 0x000b 0x000c 0x000d 0x000e 0x000f 0x0010 0x0000

1. On Master RX data , 0XFFFE received two times & last byte is not received (0xffef)

2. On Slave RX data , 0x0002 is missed , received only 15 bytes i.e. why last bytes as 0x0000

I am running default example only, and didn't modified anything regarding SPI.

What will be the problem ?

Can you suggest your ideas to solve this ?

Hi Ratheesh T,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

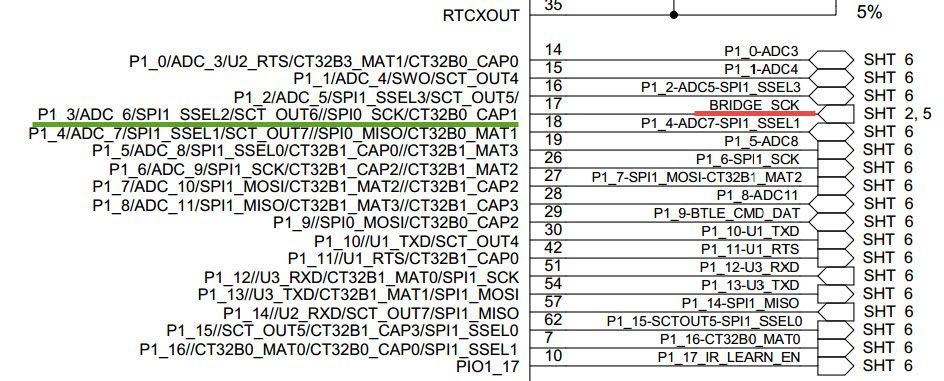

The BRIDGE_SCK pin of the J3 is assigned to the P1_3 (Fig 1). However the SPI0_SCK is assigned to the P0_11 in the periph_spi_sm_int demo.

So I think it's the root cause of your issue.

Fig 1

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi ,

Thanks for your reply.

I have tried with two options like below but issue is not solved

1.Chip_IOCON_PinMuxSet(LPC_IOCON, 1, 3, (IOCON_FUNC5 | IOCON_MODE_PULLUP | IOCON_DIGITAL_EN));

2.Chip_IOCON_PinMuxSet(LPC_IOCON, 1, 3, (IOCON_FUNC5 | IOCON_DIGITAL_EN));

It gives the same error result.

Have any other suggestion?

Hi,

Now the SPI communication is working with some restriction

i.e.

Restriction 1 -- Frequency rate reduced from 4Mhz to 1Mhz

Restriction 2 -- After every transaction if i call the function setupMaster() then only it is working fine, otherwise it is giving wrong values. But for SPI communication this function( setupMaster() ) call is not required for every transmission of data because it is only needed at the time of initialization. So please suggest me your ideas whether it is required every time or not ?

The below function shows that implementation for your reference

void spi_tx_rx(uint8_t *tx_buffer,int32_t tx, uint8_t *rx_buffer, int32_t rx)

{

volatile uint8_t *mstate;

spiMasterXfer.cbFunc = master_cb;

spiMasterXfer.state = SPIS_XFER_STATE_IDLE;

spiMasterXfer.txBuff = tx_buffer;

spiMasterXfer.txCount = tx; ///sizeof(masterTXBuffer16);// / sizeof(uint16_t);/* Count is in transfer size */

spiMasterXfer.rxBuff = rx_buffer;

spiMasterXfer.rxCount = rx; //sizeof(masterRXBuffer16);// / sizeof(uint16_t);/* Count is in transfer size */

mstate = &spiMasterXfer.state;

/* Setup master transfer options - 8 data bits per transfer, EOT, EOF */

spiMasterXfer.options = SPIM_XFER_OPTION_SIZE(8) | SPIM_XFER_OPTION_EOT | SPIM_XFER_OPTION_EOF | 0;

Chip_SPI_FlushFifos(LPC_SPIMASTERPORT);

Chip_SPIM_XferBlocking(LPC_SPIMASTERPORT, &spiMasterXfer);

while ( (*mstate != SPIM_XFER_STATE_DONE)){}

setupMaster();

}

I am using the above function like below

SPI_CS_LOW();

spi_tx_rx(masterTXBuffer16,packet_size,masterRXBuffer16,packet_size) ;

SPI_CS_HIGH();

static void setupMaster()

{

SPI_CFGSETUP_T spiSetup;

SPIM_DELAY_CONFIG_T masterDelay;

/* Initialize SPI controller */

Chip_SPI_Init(LPC_SPIMASTERPORT);

/* Call to initialize first SPI controller for mode0, master mode, MSB first */

Chip_SPI_Enable(LPC_SPIMASTERPORT);

spiSetup.master = 1;

spiSetup.lsbFirst = 0;

spiSetup.mode = SPI_CLOCK_MODE0;

Chip_SPI_ConfigureSPI(LPC_SPIMASTERPORT, &spiSetup);

/* Setup master controller SSEL0 for active low select */

Chip_SPI_SetCSPolLow(LPC_SPIMASTERPORT, 0);

/* Setup master clock rate, slave clock doesn't need to be setup */

Chip_SPIM_SetClockRate(LPC_SPIMASTERPORT, SPI_CLOCKRATE);

/* Setup master delay (all chip selects) */

masterDelay.PreDelay = 0xD;

masterDelay.PostDelay = 0xD;

masterDelay.FrameDelay = 0xD;

masterDelay.TransferDelay = 0xD;

Chip_SPIM_DelayConfig(LPC_SPIMASTERPORT, &masterDelay);

/* For the SPI controller configured in master mode, enable SPI master interrupts

for interrupt service. Do not enable SPI_INTENSET_TXDYEN. */

#if 0

Chip_SPI_EnableInts(LPC_SPIMASTERPORT, (SPI_INTENSET_RXDYEN |

SPI_INTENSET_RXOVEN | SPI_INTENSET_TXUREN | SPI_INTENSET_SSAEN |

SPI_INTENSET_SSDEN));

#endif

}

Please let me know if there's anything you'd like me to clarify