- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi,

I have a little problem on a LPC4357 running FreeRTOS 8.2.

Problem is that when I execute a SoftReset MCU restart but during EMC SDRAM initialization it stop working, with loss of LPC-Link 2 debugger control. So, no HardFault, olny stop ecxecution.

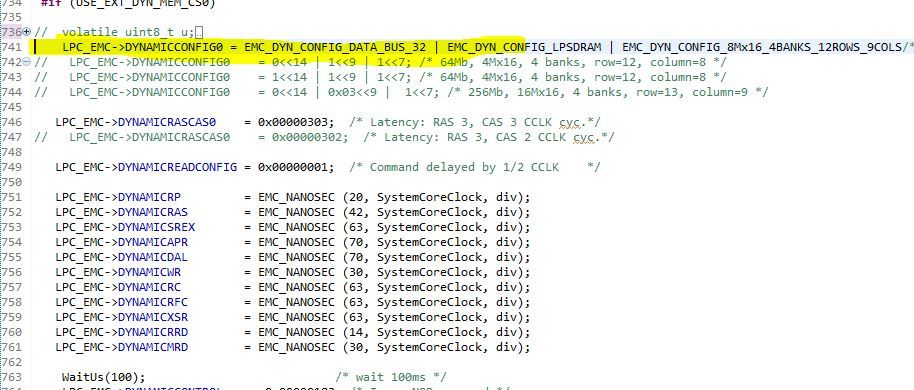

The function where CPU stop working is this: SystemInit_ExtMemCtl (void)

From some research I think it should be a Stack Pointer problem, but not sure about that, FreeRTOS Heap in my application is located in External SDRAM, and if I call the SoftReset routine before FreeRTOS start no problem with EMC init.

If I made a SoftReset after these instruction, system stop working during initialization in the Reset ISR.

The same code work right with a LPC4088 in the same condition (Ext RAM FreeRTOS Heap, same reset routine) with no problem.

In LPC 4357 I'm working only with Core M4

Thanks in advance to anyone who could help me.

已解决! 转到解答。

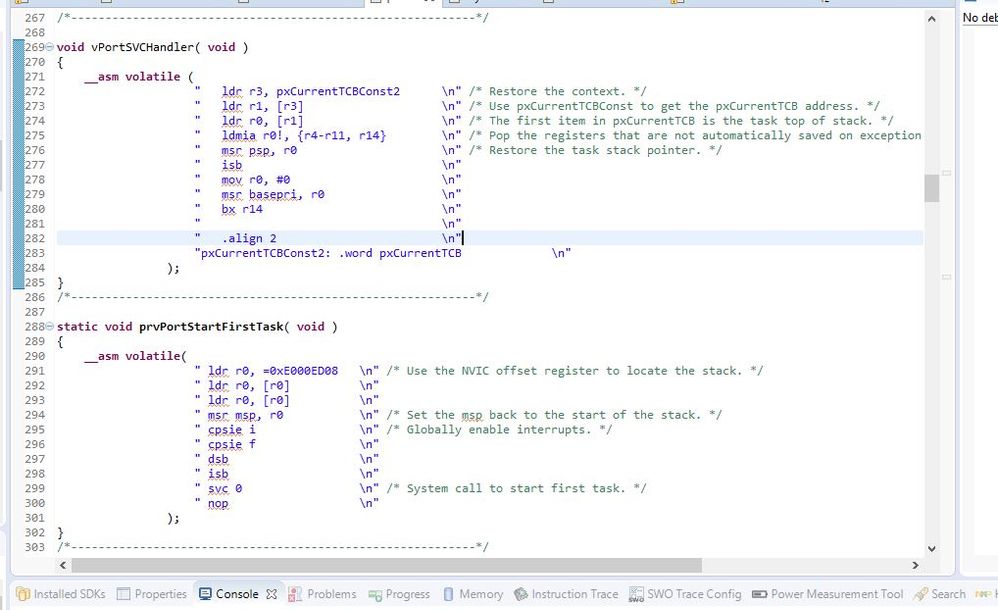

Fixed it! Below the solution, hope it helps others in future. Simply need to relocate the MSP and PSP register before resetting:

void (*user_code_entry)(void);

unsigned *p;

void SoftReset(void){

__disable_irq();

SysTick->CTRL = 0; // Disable System timer

// disable and clear pending IRQs

for (uint32_t i = 0; i < 8; i++)

{

NVIC->ICER[i] = 0xFFFFFFFF; // disable IRQ

NVIC->ICPR[i] = 0xFFFFFFFF; // clear pending IRQ

}

// Barriers

__DSB(); // data synchronization barrier

__ISB(); // instruction synchronization barrier

SCB->VTOR = 0x1A010000 & 0x1FFFFF80;

// Rebase the Stack Pointer

__set_MSP(*(uint32_t *) (0x1A010000 & 0x1FFFFF80));

__set_PSP(*(uint32_t *) (0x1A010000 & 0x1FFFFF80));

p = (unsigned *)(0x1A010000 + 4);

user_code_entry = (void *) *p;

__DSB();

__ISB();

user_code_entry();

}

Fixed it! Below the solution, hope it helps others in future. Simply need to relocate the MSP and PSP register before resetting:

void (*user_code_entry)(void);

unsigned *p;

void SoftReset(void){

__disable_irq();

SysTick->CTRL = 0; // Disable System timer

// disable and clear pending IRQs

for (uint32_t i = 0; i < 8; i++)

{

NVIC->ICER[i] = 0xFFFFFFFF; // disable IRQ

NVIC->ICPR[i] = 0xFFFFFFFF; // clear pending IRQ

}

// Barriers

__DSB(); // data synchronization barrier

__ISB(); // instruction synchronization barrier

SCB->VTOR = 0x1A010000 & 0x1FFFFF80;

// Rebase the Stack Pointer

__set_MSP(*(uint32_t *) (0x1A010000 & 0x1FFFFF80));

__set_PSP(*(uint32_t *) (0x1A010000 & 0x1FFFFF80));

p = (unsigned *)(0x1A010000 + 4);

user_code_entry = (void *) *p;

__DSB();

__ISB();

user_code_entry();

}