- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: ADC output fluctuation in LPC54608J512BD208 microcontroller

ADC output fluctuation in LPC54608J512BD208 microcontroller

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC output fluctuation in LPC54608J512BD208 microcontroller

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using LPC54608J512BD208 microcontroller in an application.

The ADC accuracy is crucial as the product is used in a Power protection segment.

I am getting fluctuations in ADC output with constant DC input. The datasheet claims max error of 4.5LSB but i am getting more than 10 counts fluctuations as shown in the results below.

| ADC channel | ADC output | |

| Min | Max | |

| ADC0_4 | 0 | 10 |

| ADC0_5 | 0 | 6 |

| ADC0_6 | 0 | 5 |

| ADC Channel | ADC Output | |

| Min | Max | |

| ADC0_5 | 2041 | 2053 |

Card 1:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2014 | 2075 | 2047 | 2051 |

| ADC0_4 | 2020 | 2064 | 2045 | 2054 | |

| ADC0_5 | 2032 | 2058 | 2046 | 2051 | |

| ADC0_6 | 2016 | 2060 | 2048 | 2056 | |

| ADC0_7 | 2021 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2018 | 2051 | 2041 | 2048 | |

Card 2:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2010 | 2066 | 2046 | 2052 |

| ADC0_4 | 2035 | 2061 | 2047 | 2054 | |

| ADC0_5 | 2031 | 2062 | 2045 | 2051 | |

| ADC0_6 | 2025 | 2059 | 2050 | 2056 | |

| ADC0_7 | 2019 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2037 | 2049 | 2041 | 2048 | |

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you have the separate and stable VDDA, and not connected to VDD ?

Have you tried to observe VDDA during the conversions, with and without the debugger ?

One should keep in mind that mixed chips like MCUs (with both analog and digital functionality) are always a compromise - usually sacrificing accuracy/noise performance for BOM costs.

A debug pod will use the internal JTAG periphery, and thus have an impact on current consumption.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi frankmeyer & xiangjun.rong,

I had started a similar query few months back on NXP forum.

https://community.nxp.com/thread/518705

I have recently shared a firmware which is causing me problem even on the development boad of NXP.

I am using OM130920 development board.

Can you look at that query as well and check if you find anything from that?

Thanks & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

From the description, I see that two factors take effect on the ADC sample fluctuation if you sample DC voltage.

1)High ADC clock frequency leads to the sample fluctuation

2)If you sample single channel, the sample fluctuation is okay. If you sample multiple channels in ONE sequence, the fluctuation for ONE DC channels is a bit big.

For the first factor, I think it is a rule that lower ADC frequency can improve the sample fluctuation. For the second factor, I am not sure.

I think it is okay from software perspective that the TSAMP bits is set up as 7, and you use 1MHz ADC clock.

BTW, I suggest you do software ADC calibration before sampling and check if it can improve the sample fluctuation.

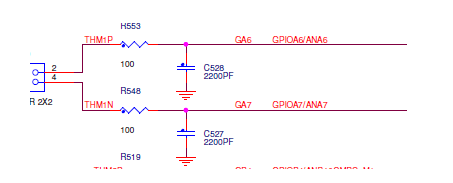

From hardware, I suggest you connect a RC(100 ohm and 2.2nF cap) circuit on each ADC analog channel.

As you know that the ADC sample fluctuation is complex, I do not guarantee it can solve the issue. anyway, pls have a try.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun.rong,

1) I have tried changing the ADC clock to 1 MHz and 500 KHz but no improvement.

I have attached the firmware for 1 MHz ADC clock for OM13092 board.

Can you please check the code at your board.

I have attached the picture of the test set up as well.

I have connected ground as input to ADC0_4 channel.

2) Ideally, entire sequence sampling also should not cause any problem as per the ADC specifications of LPC546.

Thanks & best regards,

Prasanna