- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso软件和工具

- :

- Kinetis软件开发套件

- :

- K64F DSPI Clock Glitch (KSDK SPI Master Driver)

K64F DSPI Clock Glitch (KSDK SPI Master Driver)

K64F DSPI Clock Glitch (KSDK SPI Master Driver)

Hi there,

I'm just looking to test out some simple DSPI Master transfers (non-DMA operation) on the FRDM-K64F using the KSDK (1.0.0) Master peripheral driver.

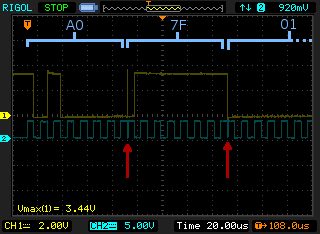

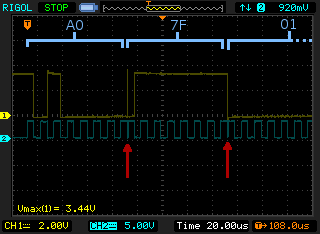

The API seems pretty straight-forward. However, with in each byte in my transfers, there's a glitch between bit 0 and bit 7 of the following byte:

This only appears to happen for the kDspiClockPhase_FirstEdge clock phase option.

I was just curious if anyone else has run into this. The code's attached.

Cheers,

Jon

Original Attachment has been moved to: main.c.zip

A colleague of mine kindly pointed out that I have overlooked the DSPI_DRV_MasterSetDelay() API function. Using this with the kDspiAfterTransfer option) has allowed me to introduce time between successive words within a transfer.

I'll have to take a look at the datasheet and the peripheral driver to understand why I needed to do this for kDspiClockPhase_FirstEdge, but not kDspiClockPhase_SecondEdge....will try to report back here, if anyone is interested.

Just as another minor note -- I see the data is idling high, hence that momentary spike between data byte 0 and data byte 1 in my previous screenshot.

- Jon

I am experiencing the same behavior under the same conditions. Was DSPI_DRV_MasterSetDelay() the ultimate fix, or did you uncover anything else?