- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Re: FRDM-KL43 FlexIO Register viewing on "EmbSys Register window"

FRDM-KL43 FlexIO Register viewing on "EmbSys Register window"

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FRDM-KL43 FlexIO Register viewing on "EmbSys Register window"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

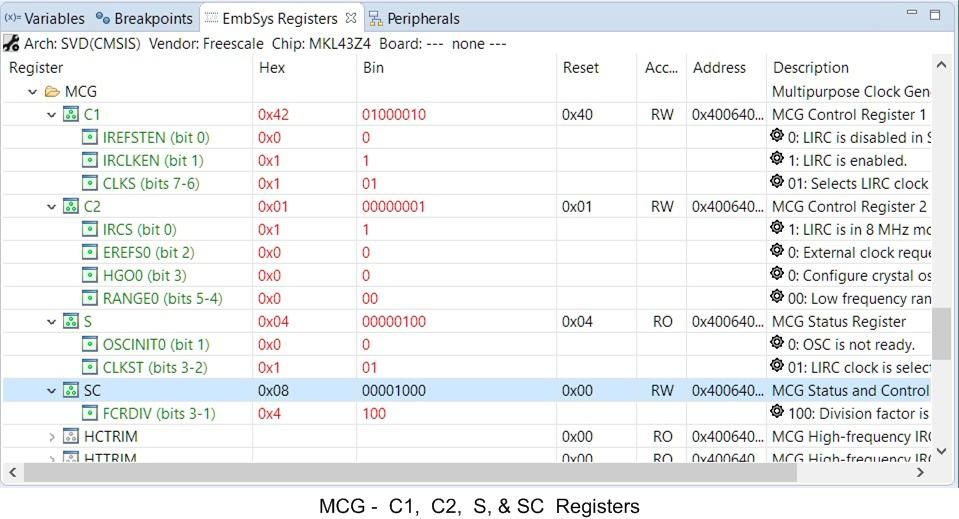

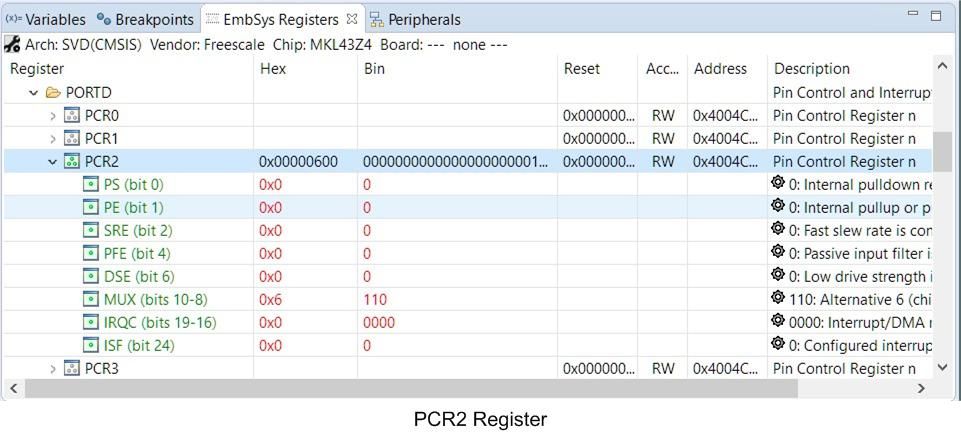

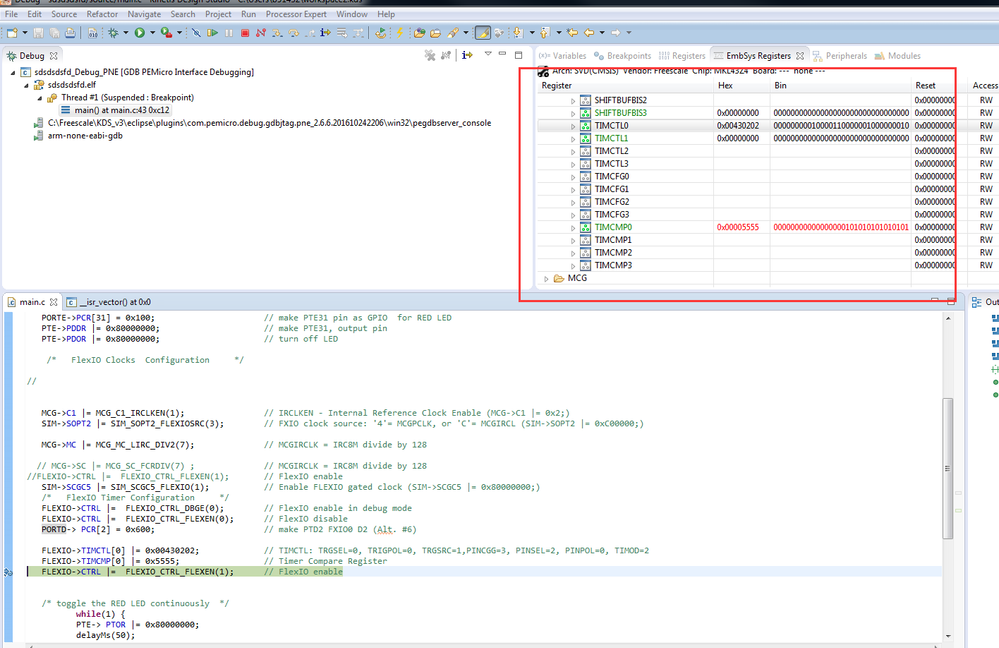

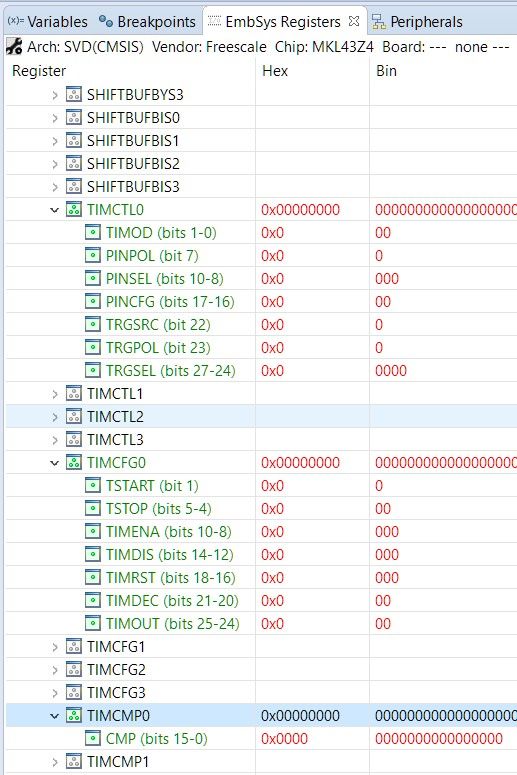

I can’t read FlexIO registers during debugging using "EnbSys Register" window view.

I’m using KDS 3.2 & KSDK v2 and P&M SDA to evaluate FlexIO on FRDM-KL43Z board.

I wrote two PWM simple test programs, one that uses API and the other direct FlexIO register configuration (Bare-metal).

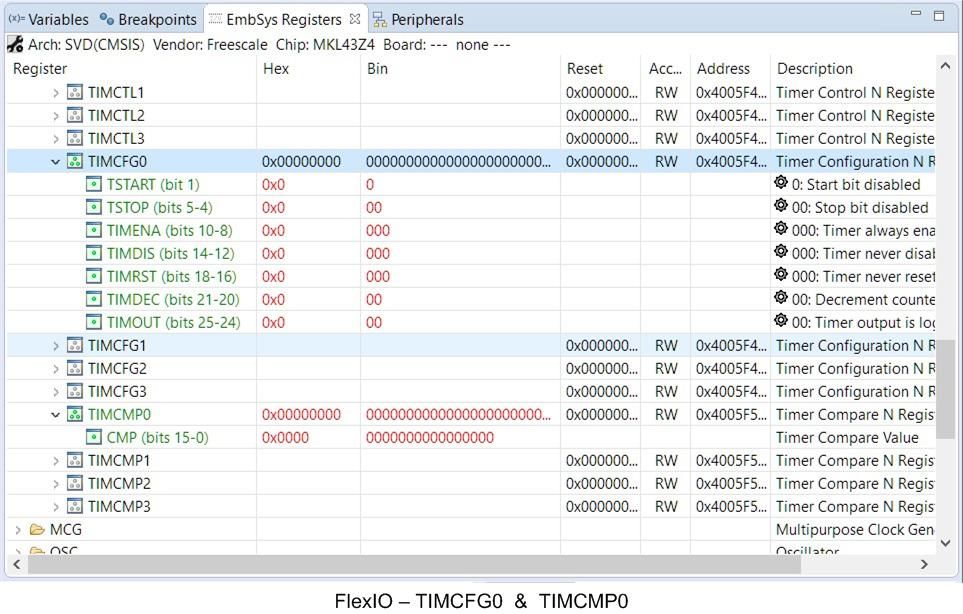

Reading FlexIO registers fails in both test it returns zero result.

As you can see at the same time reading other peripheral is O.K

Using API I have problem no output (probably configuration).

The Bare-metal program is working well I have output on PTD2 pin.

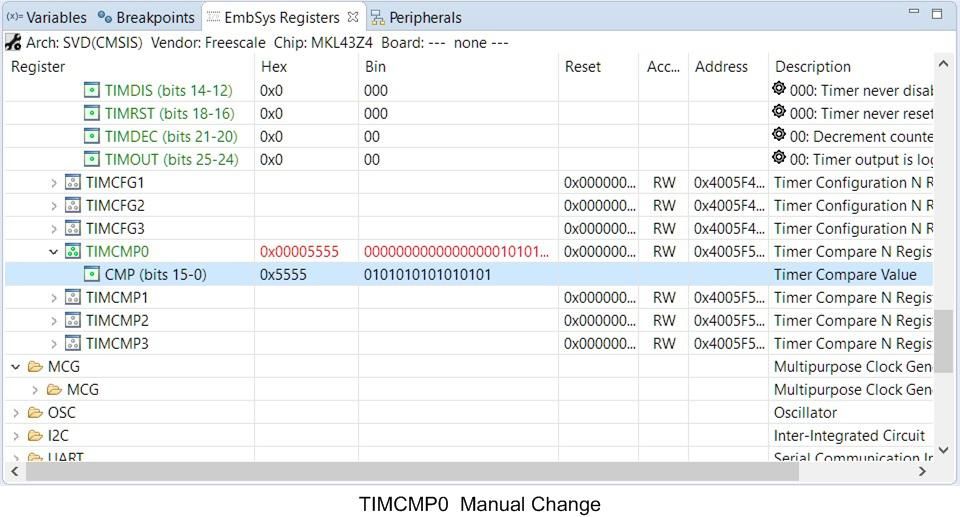

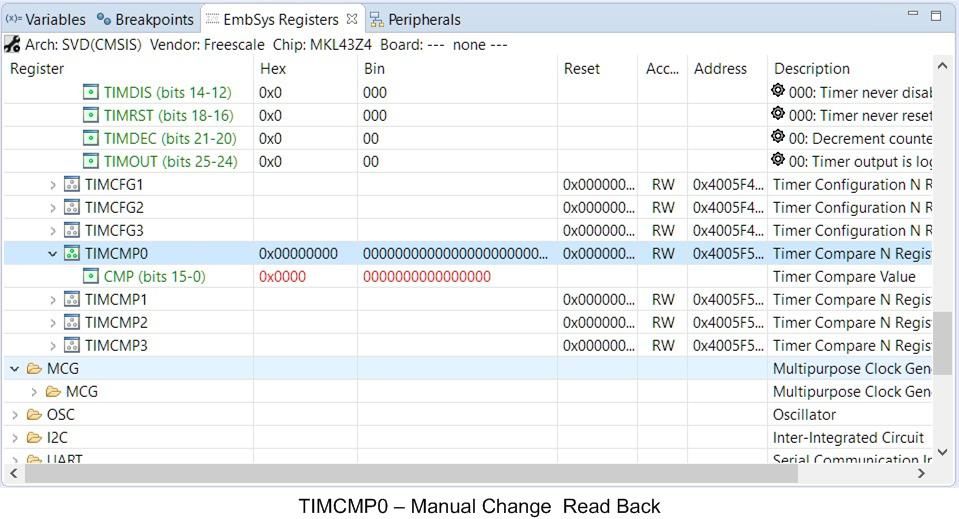

Using “not working” FlexIO display I have changed manually TIMCMP value from 0x7474 to 0x5555. The change has been accepted and PWM cycle has been changed.

Reading again this register returns again zero value.

B.R

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

All,

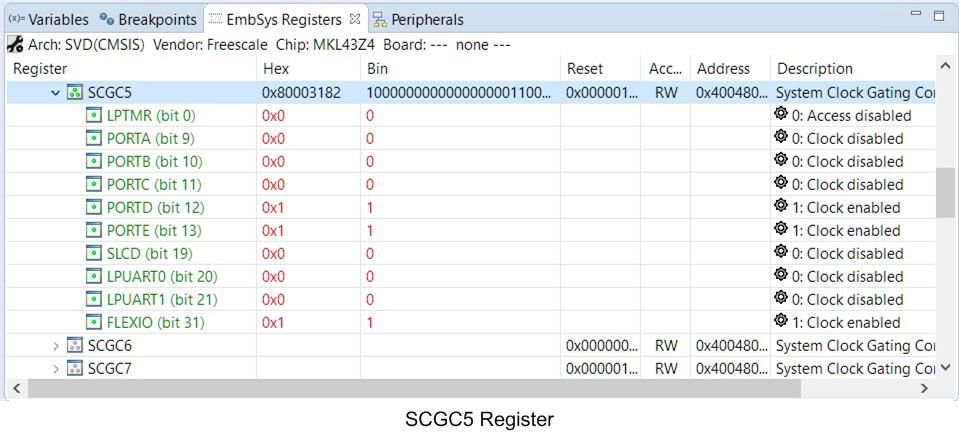

Official new errata statement (1N71K mask set):

FlexIO: Reading FlexIO register when FlexIO functional clock is disabled

results in a bus hang

Description: Accessing a FlexIO register when the FlexIO functional clock is disabled will hang the

bus and the access will stall forever.

Workaround: Always enable the FlexIO functional clock before accessing any FlexIO register.

This statement is also valid if customer has opened an register window during debugging. The register window should be opened after clock enabled.

regards

R.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you be more specific where I didn't find any PCC_FLEXIO0[PCS] description in KL43 Sub-Family Reference Manual

In my application FlexIO clock is MCGIRCLK and in my understanding is always enabled.

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shaul,

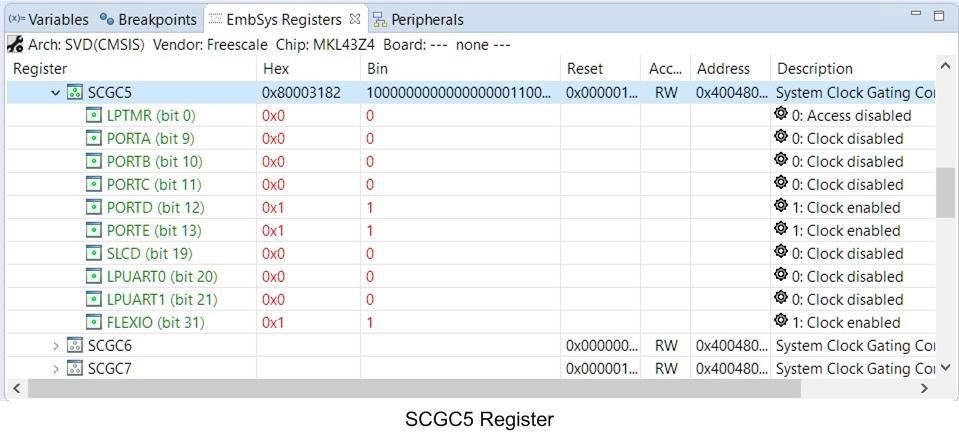

sorry, it was mistake in nameing. In general it means that if the FlexIO is not clocked yet - means SIM_SCGC5 has disabled FLIEXIO bit field.

regards

R.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

It's not my case.

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello shaul,

The problem is not the clock , it is PE debug firmware , also sorry my mistake.

Please change the debug mode to Jlink on board , then when set to 128 128 ,

it also can work well .

I attached the jlink firmware , please copy and paste it into the bootloader of board .

The detail steps you can refer to "Updating the OpenSDA Firmware.pdf", I also attached it .

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice;

Thanks !!!

Do you have the same firmware for PE_Micro?

Have verified it also on KL82 and K82?

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul,

The PE_Micro firmware have problem , so we failed before , i have not the another one .

About the KL82 and K82 , sorry i have not the board, i also attached the firmware for Jlink

for the two boards , you can test it .

This is the linker for Jlink firmware : SEGGER - The Embedded Experts - Downloads - J-Link / J-Trace .

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

Can you please send me yours test.

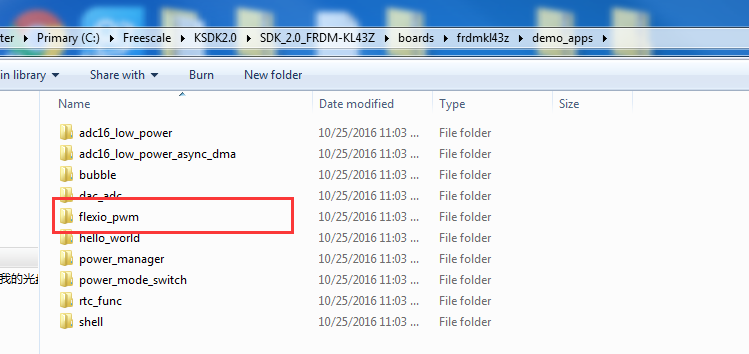

In my SDK_2.0_FRDM-KL43Z\boards\frdmkl43z\demo_apps\flexio_pwm there is no such project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul,

- It seems you open the package for KL25 device ,while you use the KL4.

This it your screenshot :

Please search the demo under :

- And yes, i have run your project , when it run into the code about FlexIO, it will crash.

I think maybe it lack some configuration in the initialize code. maybe something else.

Please debug step by step and refer to the demo code to check. I will also help you

to check , when find the reason, i will show you , also please tell me when you resolve it.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice

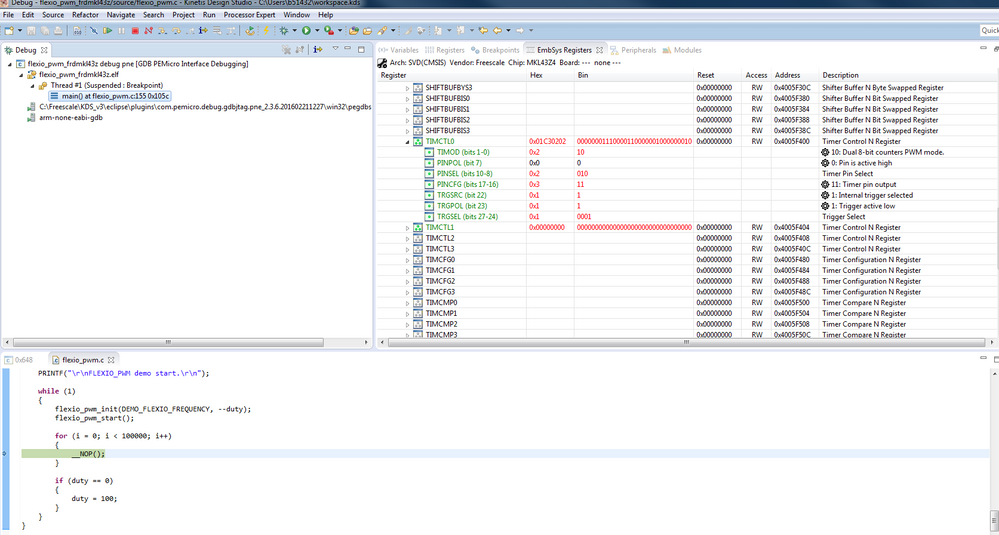

I looked in NXP demo “flexio_pwm_frdmkl43z.

This demo is using RC48M as a source clock for FLEXIO.

In my test I’m using MCGirCLK clock as a source (to use divisions).

Please change the code at “flexio_pwm.c “ line #110.

From CLOCK_SetFlexio0Clock(1U); to to CLOCK_SetFlexio0Clock(3U); The reading from FLEXOI registers returns zero.

I also replaced flexio_pwm.c with my main.c and with the same results.

I’m attaching my main.c.

Regards

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul

Please test the attachment , i changed based on our code . On my side , it can work well :

Please pay attention two points , : first one after finish configure the clock(SIM and MCG regiter)

then enablle the FLEXIO clock ;second , you confgure the clock divider all to 128, the clock is too slow .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice

Thanks again

Sorry you didn’t solve the problem.

In my project MCGIRCLK is used as Timer source clock.

This clock is divided by two dividers MCG_MC[LIRC_Div2] and MCG_SC[FCRDIVthat can be configure by :

1. BOARD_BootClockRUN() (file clock_config.c) or

2. directly by

a. MCG->MC |= MCG_MC_LIRC_DIV2(7); // MCGIRCLK = IRC8M divide by 128

b. MCG->SC |= MCG_SC_FCRDIV(7) ; // MCGIRCLK = IRC8M divide by 128

Doesn’t matter how you configure it in my opinion there is a problem with combination of those two dividers.

Doing few tests I found that the combination of 128 x 128 for DIV2 and FRCDIV is not working.

If for example you will configure it to 128 x 1 or 1 x 128 it will work and this is your working test.

Because writing to MCG register is working you can do simple manual test.

You can change divider values at break point, then run and break point again and see the result if there is flexio read zero or it is OK.

So to summarize it, the question is if there are any limitations on this clock?

BR

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul,

Sorry i have not find the authoritative explain about he FlexIO clock low limit.

Now you can only decrease the divider to increase the clock , for it can work well .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul,

Please define one variable in your code to read the registers about FlexIO ,

check whether they are 0 .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice

I want to notify that writing to Timer CMP register manually contents is modified and I can see the result on oscilloscope. Reading back from the register returns again “zero”.

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Shaul,

- I think it is not the problem of "EmbSys Registers" view, please check the initialize of you FLEXIO code .

- It seems you use the KSDKv2.0 lib , there is a FlexIO_pwm demo under KSDK v2.0 , please refer

to it : SDK_2.0_FRDM-KL43Z\boards\frdmkl43z\demo_apps\flexio_pwm

I test it on my side , the register can work well :

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice

I build again FRDM-KL43 package and there is your working demo.

Probably my package was old.

This demo is using API and my test is direct peripheral registers configuration.

I will try to understand, probably in my configuration something is missing.

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice

I’m attaching my working main.c file

While program is in “Suspend” All registers are visible accept FlexIO perifheral.

I’m attaching also my screen captures with register views.