- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- API to configure SIM_SOPT2[FLEXIOSRC]

API to configure SIM_SOPT2[FLEXIOSRC]

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

To select FlexIO clock source using direct register access is very simple

SIM->SOPT2 |= SIM_SOPT2_FLEXIOSRC(x) , “x” can be 01, 10,11.

I’m looking for something equivalent using API.

Where it is defined in Kinetis SDK v.2.0 API Reference Manual?

BR

Shaul

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

I looked at the flexio_i2c_read_accel_value_transfer_frdmkl27z example in KSDK_v2.

It has following:

CLOCK_SetFlexio0Clock(1U);

This is defined in fsl_clock.h as:

/*!

* @brief Set FLEXIO clock source.

*

* @param src The value to set FLEXIO clock source.

*/

static inline void CLOCK_SetFlexio0Clock(uint32_t src)

{

SIM->SOPT2 = ((SIM->SOPT2 & ~SIM_SOPT2_FLEXIOSRC_MASK) | SIM_SOPT2_FLEXIOSRC(src));

}

And MKL27Z644.h has:

#define SIM_SOPT2_FLEXIOSRC(x) (((uint32_t)(((uint32_t)(x)) << SIM_SOPT2_FLEXIOSRC_SHIFT)) & SIM_SOPT2_FLEXIOSRC_MASK)

Hope this helps.

Regards,

David

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello David;

Thanks

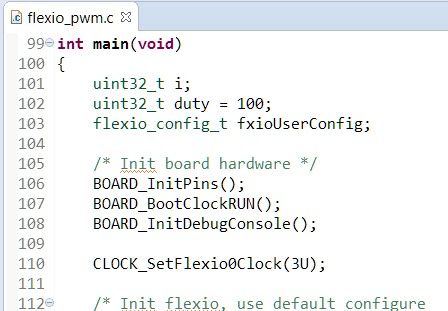

Run with FlexIO = 3U line 110

Run with FlexIO = 1U

I'm using windows 10

PEMicro : MSD-DEBUG-FRDM-KL43Z48M_Pemicro_v118.SDA

BR

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

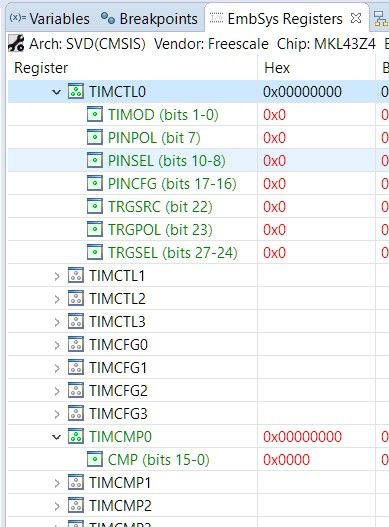

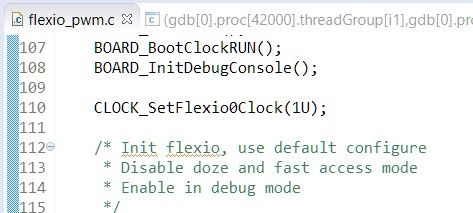

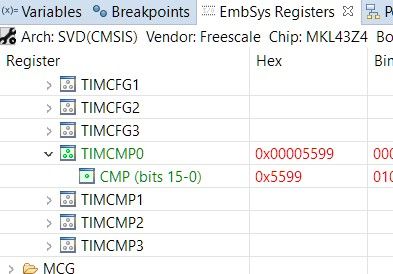

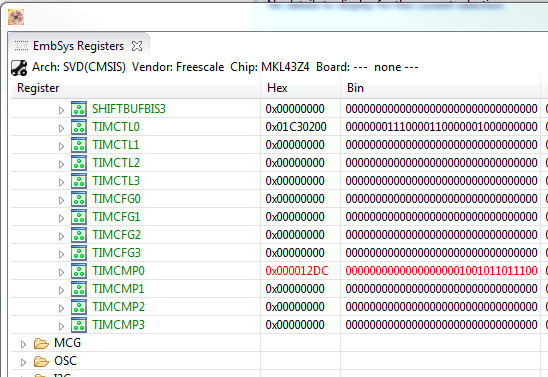

I can read the registers and see them update when I hit breakpoint with either clock configuration (1 or 3).

I'm still wondering if your KSDK is slightly older than mine.

To test I cloned the example as an standalone project.

Un-Zip to : C:\NXP\KSDK_v2\SDK_2.0_FRDM-KL43Zb_KDS\boards\frdmkl43z\user_apps

Have a breakpoint set at line 151 of flexio_pwm.c, open the EmbSys Registers window and see if you see TIMCMP0 updates:

This is with line 137 set to: CLOCK_SetFlexio0Clock(3U); //DES was (1U);

Regards,

David

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello David

Thanks for your support

In my application I’m using FRCDIV and LIRC_DIV2 to get low PWM Duty Cycle.

By doing few experiments with FRCDIV and LIRC_DIV2 setup, I found that if total division is greater than 128 x 2 or 2 x 128 I can’t read FlexIO registers.

I tried this on flexio_pwm_frdmkl43z demo and my bare-metal test.

In my test I have used KExTools v2 for pin_mux and clock_config generation.

I have also replaced the flexio_pwm.c with my code I got same behavior.

Is there any restriction on total division generated by FRCDIV and LIRC_DIV2?

Regards

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

I do not know if there are limitations on those clock dividers. Seems empirically there are from your experimentations. But I will ask around.

Are you setting the FASTACC bit to "1" in the FLEXIO_CTRL? If yes I see a note that says FlexIO clock should be at least twice the bus frequency.

Regards,

David

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello David

Alice Yang suggested solution is to use J_Link for debug.

There is a problem with PE firmware.

Thanks for your help

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello David

Using this API I can change FlexIO clock but there is a problem in debug mode when you use MCGIRCLK reading FlexIO registers returns zero. Reading from SIM or MCG is OK.

I have the problem in my test and I have verified it using NXP demo “flexio_pwm_frdmkl43z4” by changing the clock at line #110 of the source code.

BR

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

Hmmm.

Is the SIM_SOPT2[FLEXIOSRC]=3 when you are trying to read the FlexIO registers?

My clock config for the FlexIO is at line 137:

CLOCK_SetFlexio0Clock(3U); //DES was (1U);

I just downloaded this KSDK_v2 for frdmkl43z. I wonder if it is newer than your version?

I am able to see the FlexIO registers in the EmbSys Regiser window. I tried both PEMicro and JLink successfully.

Second

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

David I forgot to mention that the problem is reading.

Writing to FlexIO register is O.K.

The same problem I have with my bare-metal program that I wrote.

I have PWM output and I can change duty cycle by writing to CMP register.

Regards

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi shaul dorf,

hope you are doing great. please check this Kinetis SDK 2.0 API Reference Manual: FlexIO Driver

the

| void FLEXIO_Init | ( | FLEXIO_Type * | base, |

| const flexio_config_t * | userConfig | ||

| ) |

and check the flexio_config_t what is inside this structure might be what you are looking for. please let me know if this helped your problem.

Have a great day.

Best regards.

-Jonathan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello and Thanks;

Maybe I didn’t understand this structure wee but I think that it covers only FLEXIO_TIMCTC, TIMCFG and TIMCMP.

My problem is with SIM_SOPT2[FLEXIOSRC] field where Flex|IO clock is defined.

B.R

Shaul

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shaul,

I looked at the flexio_i2c_read_accel_value_transfer_frdmkl27z example in KSDK_v2.

It has following:

CLOCK_SetFlexio0Clock(1U);

This is defined in fsl_clock.h as:

/*!

* @brief Set FLEXIO clock source.

*

* @param src The value to set FLEXIO clock source.

*/

static inline void CLOCK_SetFlexio0Clock(uint32_t src)

{

SIM->SOPT2 = ((SIM->SOPT2 & ~SIM_SOPT2_FLEXIOSRC_MASK) | SIM_SOPT2_FLEXIOSRC(src));

}

And MKL27Z644.h has:

#define SIM_SOPT2_FLEXIOSRC(x) (((uint32_t)(((uint32_t)(x)) << SIM_SOPT2_FLEXIOSRC_SHIFT)) & SIM_SOPT2_FLEXIOSRC_MASK)

Hope this helps.

Regards,

David

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello David;

Thanks !!!

This function that belongs to SIM register is defined in Clocks driver chapter #6 of the API ref. manual.

API is defined in fsl_clock.h, but for the "src" value you have to use hardware reference manual.

My suggestion is to improve documentation or to prepare white paper about clocks configuration issues.

Thanks again.

BR

Shaul