- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: kinetis spi driver, artificially hold the spi line low (to wake the device before communication)

kinetis spi driver, artificially hold the spi line low (to wake the device before communication)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When using the kinetis spi driver and processor expert is there a way to artificially hold the spi line low (to wake the device before communication). I am using a mkl27

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bud

The KL27 has DMA, which can be triggered by the SPI flags.

However the SPI is double-buffered so as long as you keep the buffer full you shouldn't have any gaps between bytes in a sequence.

That is, fill the next byte to be sent when the TX buffer full flag is not set and read out the received data on the RX buffer not empty flag - don't do the Tx on the Rx buffer empty flag otherwise there may be a gap due to the internal synchronisation (which is probably always there on the start byte).

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bud

Unlike the SPI in the K family, the one in the KLs has very little chip select control in master mode.

It is probably easiest to use the pin in GPIO mode, negate it and program a delay (eg. using timer and interrupt) before starting the SPI transmission.

Regards

Mark

Kinetis: http://www.utasker.com/kinetis.html

KL27: http://www.utasker.com/kinetis/FRDM-KL27Z.html / http://www.utasker.com/kinetis/Capuccino-KL27/Capuccino-KL27.html

For the complete "out-of-the-box" Kinetis experience and faster time to market

:smileyinfo: Out-of-the-box support for 47 Kinetis boards and 10 IDEs (460 combinations from a single code source with no porting required)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

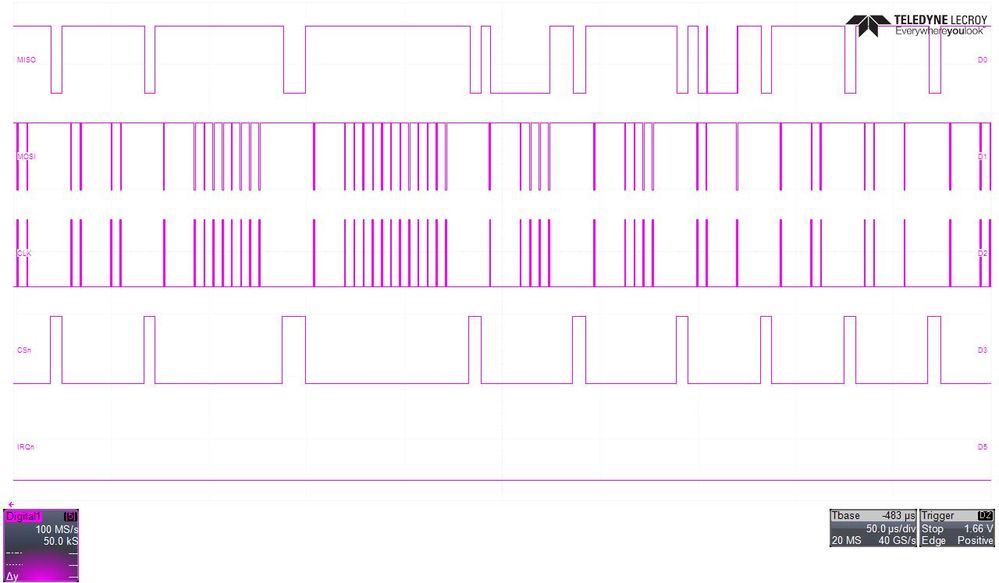

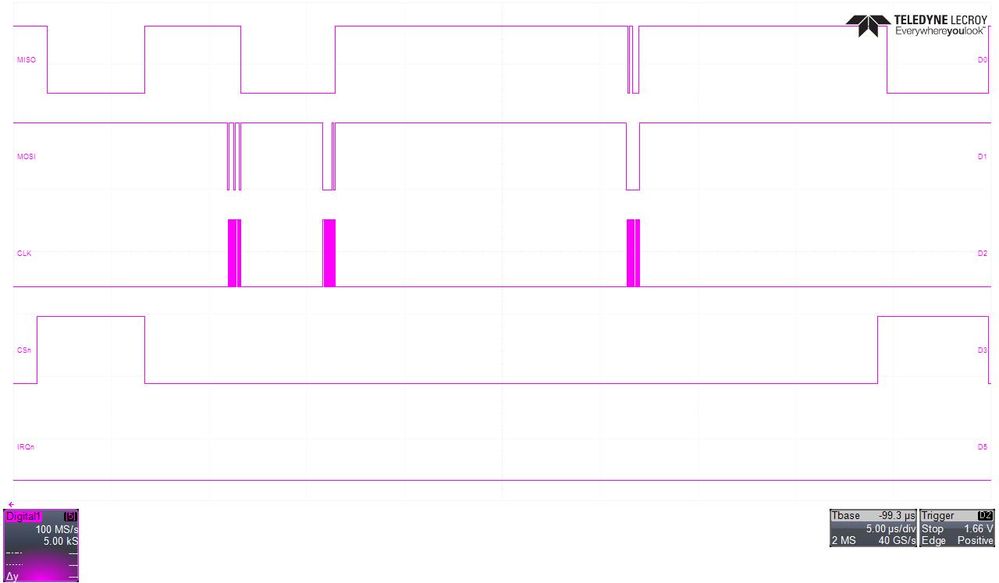

I was hoping that was not the case as there is a 4.26us delay after the cs goes low and the first spi clock and a 11.52us delay after the last spi clock before the cs returns high (12Mbit/s). i do however see the same 4.26us delay between bytes. this chip does not seem to have dma, is there any way to speed this up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bud

The KL27 has DMA, which can be triggered by the SPI flags.

However the SPI is double-buffered so as long as you keep the buffer full you shouldn't have any gaps between bytes in a sequence.

That is, fill the next byte to be sent when the TX buffer full flag is not set and read out the received data on the RX buffer not empty flag - don't do the Tx on the Rx buffer empty flag otherwise there may be a gap due to the internal synchronisation (which is probably always there on the start byte).

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you