- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- XTAL pins capacitance

XTAL pins capacitance

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are checking our crystal parameters and we are wondering what are the XTAL pins capacitance on the MKE16FVLH16 µC.

the capacitance is not specified in the datasheet, so we looked at the IBIS model, to see that the specified value is about 0.334pF. This value seems very low. We can see that it is about the same for all other pins, but in the datasheet it is stated that digital pins usually have a 7pF capacitance, so we don't know what value to use.

What is the capacitance value for XTAL pins ?

What is the value expressed in the IBIS file ?

Thank you in advance,

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @simongodfrind ,

C_pkg is for those pins who haven't C_pin. Pin11 needn't C_pkg.

C_comp is different with C_pkg/C_pin. C_comp is model cap or die cap. You can add it.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's not a good answer. Please read the question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @simongodfrind ,

I asked to designer. They said the ibis module is got by simulation. This value should be used to calculate XTAL CL. Cin_a in Capacitance attributes table should not be used.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jing,

Thank you for your answer but I need the advice from your team to size the right c_load for the crystal circuit in order to robustify our design before production. I understand that those values are not at hand.

According to your datasheet :

So, as stated, we check the crystal manufacturer user manual and datasheet and it says this :

So we lack Cin and Cout. As you can see our question is legitimate and is not answered in the datasheet nor in this forum yet.

We would like to know what are Cin and Cout (should be different).

According to the ibis file the values seems very small (0.3pF+0.3pF? ; 0.3pF+0.4pF?), in other datasheet I am used to see (4->7pF; 7->12 pF), (4 pF; 9 pF), (9 pF; 10 pF) or (5 pF; 10 pF).

Could you please investigate ?

It is a matter of being able to start the crystal over our temperature range and at the right frequency.

Sincerely,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"...order to robustify our design before...It is a matter of being able to start the crystal over our temperature range and at the right frequency."

Really the minutiae of such tiny capacitances don't make any difference compared to the board parasitics and the real world tolerances of real capacitors.

If you really want robustness, use a MEMs and not a crystal.

If forced to use a crystal and want to make sure it ALWAYS starts, put a 10 Meg resistor across the crystal, place a current limiting resistor on the XOut pin and make sure the two external load capacitors have slightly different values. Take what the Crystal Manufacture recommends and change the value of each by a few pf in opposite directions. May have to swap sides if frequency is a bit off.

Failing physical failures from overdrive or being dropped, what causes the oscillator to not start is that Murphy's Law has everything perfectly balanced on both XOut and XIn. The 10 Meg resistor and unbalanced loading caps prevent this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In fact it depends on the order of board parasitics (depends on layout, planes and stackup) and the order of C_in, C_out. Which I would like to know they value to confidently neglect them or not. Moreover if bad tolerances occurs despites our requirement, I would consider it as a parallel problem to assess.

My concern is that almost half of the paper I see suggest to take into account C_in and C_out. Because they claim C_in and C_out might not be negligible unfortunately (cf. previous message).

I hear you well that from your point of view they are negligible (let's find out with the help of @jingpan) compared to board parasitics and tolerances.

If they are negligible that do not make any sense to use them I agree, if not it might reduce my C_load of 23%.

Thank you for your point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @simongodfrind ,

Please use the data in ibis. In our application notes, the capacitance of the pin itself is basically ignored.

https://www.nxp.com/docs/en/application-note/AN3208.pdf

https://www.nxp.com/docs/en/application-note/AN1706.pdf

https://www.nxp.com/docs/en/application-note/AN1783.pdf

Among these docs, AN1783 is the most important I think.

Crystal oscillator circuit provides stable oscillations when gmXOSC > 5 * gm_crit. The gm_crit is defined as:

gm_crit = 4 * ESR * (2πF)2 * (C0 + CL)2

where:

1 gmXOSC is the transconductance of the internal oscillator circuit

2 ESR is the equivalent series resistance of the external crystal

3 F is the external crystal oscillation frequency

4 C0 is the shunt capacitance of the external crystal

5 CL is the external crystal total load capacitance. CL = Cs+ [C1*C2/(C1+C2)]

6 Cs is stray or parasitic capacitance on the pin due to any PCB traces

7 C1, C2 external load capacitances on EXTAL and XTAL pins

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jingpan ,

Thank you for your prompt answer incl. the stability criteria.

I understand that the procedure recommended by NXP papers neglect Cin, Cout and if I want to include them, you would recommend me to use the one from the IBIS file.

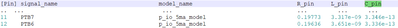

So here is my last question about this IBIS file, could you please verify my understanding?

1) I would use the C_pin given at the pin 11:EXTAL and 12:XTAL (as we have the 64 LQFP)

that have 3.346e-13 and 3.336e-13F respectively.

2) But do I have to take into account C_pkg, or add it?

3) Do I have to take into account C_comp typical, or add it?

3.1) If I follow the model definition of p_io_5ma_model -> p_io_5p0_5ma as we use 5V

3.2) If I follow the model definition of p_io_5ma_model -> p_io_3p3_5ma as I saw the clk waveform is under 3.3V

Thank you for your answer,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @simongodfrind ,

C_pkg is for those pins who haven't C_pin. Pin11 needn't C_pkg.

C_comp is different with C_pkg/C_pin. C_comp is model cap or die cap. You can add it.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

@jing, according to your answer, that means we have to reduce our loading capacitor of 5.3% compared to the recommended simplified dimensioning rules. Thus, if the IBIS file is accurate enough and the interpretation are correct, Cin and Cout could be, in fact, neglected in most cases (as anticipated by @bobpaddock).

Thank you for the investigation and your time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content