- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Wrong clock settings on K70.

Wrong clock settings on K70.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Wrong clock settings on K70.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I work with TWR-K70F120M.

I have an IAR project. The clocks calculated as in sysinit().

#elif defined (SYNCH_MODE)

/* Set the system dividers */

/* NOTE: The PLL init will not configure the system clock dividers,

* so they must be configured appropriately before calling the PLL

* init function to ensure that clocks remain in valid ranges.

*/

SIM_CLKDIV1 = ( 0

| SIM_CLKDIV1_OUTDIV1(0)

| SIM_CLKDIV1_OUTDIV2(2)

| SIM_CLKDIV1_OUTDIV3(2)

| SIM_CLKDIV1_OUTDIV4(5) );

/* Initialize PLL1 */

/* PLL1 will be the source MCGOUT and the DDR controller */

mcg_clk_hz = pll_init(OSCINIT, /* Don't init the osc circuit, already done */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_1, /* PLL to initialize, in this case PLL1 */

PLL1_PRDIV, /* PLL predivider value */

PLL1_VDIV, /* PLL multiplier */

MCGOUT); /* Don't use the output from this PLL as the MCGOUT */

/* Check the value returned from pll_init() to make sure there wasn't an error */

if (mcg_clk_hz < 0x100)

while(1);

/* Initialize PLL0 */

/* PLL0 is initialized, but not used as the MCGOUT */

pll_0_clk_khz = (pll_init(NO_OSCINIT, /* Initialize the oscillator circuit */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_0, /* PLL to initialize, in this case PLL0 */

PLL0_PRDIV, /* PLL predivider value */

PLL0_VDIV, /* PLL multiplier */

PLL_ONLY) / 1000); /* Use the output from this PLL as the MCGOUT */

/* Check the value returned from pll_init() to make sure there wasn't an error */

if ((pll_0_clk_khz * 1000) < 0x100)

while(1);

pll_1_clk_khz = mcg_clk_hz / 1000;

#else

#error "A PLL configuration for this platform is NOT defined"

#endif

/*

* Use the value obtained from the pll_init function to define variables

* for the core clock in kHz and also the peripheral clock. These

* variables can be used by other functions that need awareness of the

* system frequency.

*/

mcg_clk_khz = mcg_clk_hz / 1000;

core_clk_khz = mcg_clk_khz / (((SIM_CLKDIV1 & SIM_CLKDIV1_OUTDIV1_MASK) >> 28)+ 1);

periph_clk_khz = mcg_clk_khz / (((SIM_CLKDIV1 & SIM_CLKDIV1_OUTDIV2_MASK) >> 24)+ 1);

/* For debugging purposes, enable the trace clock and/or FB_CLK so that

* we'll be able to monitor clocks and know the PLL is at the frequency

* that we expect.

*/

trace_clk_init();

fb_clk_init();

/* Initialize the DDR if the project option if defined */

#ifdef DDR_INIT

twr_ddr2_script_init();

#endif

For TWR-K70F120M clock should be 120 Mhz. But I get 150 Mhz.

mcg_clk_khz = 150000

core_clk_khz = 150000

periph_clk_khz = 50000

I have another IAR project. In the second project I get the right value - 120 Mhz.

mcg_clk_khz = 120000

core_clk_khz = 120000

periph_clk_khz = 60000

Comparing these functions - sysinit() I didn't find any difference. What could be a problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Evgeny,

It should be still caused by your code configuration.

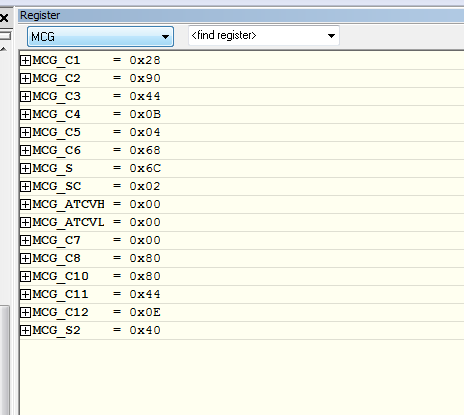

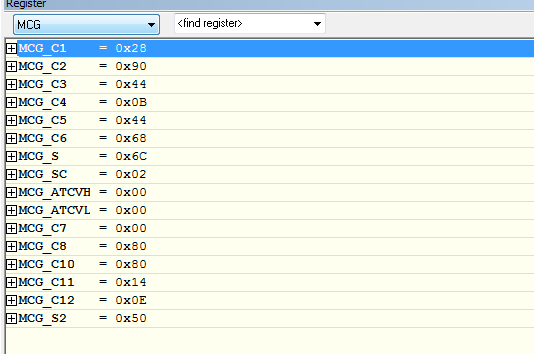

You can compare the MCG register to check what the difference between these two projects, and also you can post the register data, I will help you to check it.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Thank you for the answer. MCG register is set in

/* Initialize PLL0 */

/* PLL0 will be the source for MCG CLKOUT so the core, system, FlexBus, and flash clocks are derived from it */

mcg_clk_hz = pll_init(OSCINIT, /* Initialize the oscillator circuit */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_0, /* PLL to initialize, in this case PLL0 */

PLL0_PRDIV, /* PLL predivider value */

PLL0_VDIV, /* PLL multiplier */

MCGOUT); /* Use the output from this PLL as the MCGOUT */

/* Initialize PLL1 */

/* PLL1 will be the source for the DDR controller, but NOT the MCGOUT */

pll_1_clk_khz = (pll_init(NO_OSCINIT, /* Don't init the osc circuit, already done */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_1, /* PLL to initialize, in this case PLL1 */

PLL1_PRDIV, /* PLL predivider value */

PLL1_VDIV, /* PLL multiplier */

PLL_ONLY) / 1000); /* Don't use the output from this PLL as the MCGOUT */

The defines in both projects the same

#define OSCINIT 1

#define OSC_0 0

#define CLK0_FREQ_HZ 50000000

#define LOW_POWER 0

#define CLK0_TYPE CANNED_OSC

#define PLL_0 0

#define PLL_1 1

#define PLL0_PRDIV 5

#define PLL0_VDIV 24

#define PLL_ONLY 0

#define PLL1_PRDIV 5

#define PLL1_VDIV 30

#define MCGOUT 1

So MCG should the same. When I compare the MCG registers – it different.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Evgeny Erenburg,

Your problem is still caused by your configuration.

Please refer to the TWR-K70F120M sample code from the official website:

Kinetis 120MHz bare metal sample code

If you compare with your code, it is not difficult to find your problem:

1.

mcg_clk_hz = pll_init(OSCINIT, /* Don't init the osc circuit, already done */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_1, /* PLL to initialize, in this case PLL1 */

PLL1_PRDIV, /* PLL predivider value */

PLL1_VDIV, /* PLL multiplier */

MCGOUT); /* Don't use the output from this PLL as the MCGOUT */

2.

mcg_clk_hz = pll_init(OSCINIT, /* Initialize the oscillator circuit */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_0, /* PLL to initialize, in this case PLL0 */

PLL0_PRDIV, /* PLL predivider value */

PLL0_VDIV, /* PLL multiplier */

MCGOUT); /* Use the output from this PLL as the MCGOUT */

Please check the head file on your side:

#define PLL0_PRDIV 5

#define PLL0_VDIV 24

#define PLL1_PRDIV 5

#define PLL1_VDIV 30

The parameter is not the same.

So, if you want to get the 12Mhz core clock, just refer to the official sample code:

mcg_clk_hz = pll_init(OSCINIT, /* Initialize the oscillator circuit */

OSC_0, /* Use CLKIN0 as the input clock */

CLK0_FREQ_HZ, /* CLKIN0 frequency */

LOW_POWER, /* Set the oscillator for low power mode */

CLK0_TYPE, /* Crystal or canned oscillator clock input */

PLL_0, /* PLL to initialize, in this case PLL0 */

PLL0_PRDIV, /* PLL predivider value */

PLL0_VDIV, /* PLL multiplier */

MCGOUT); /* Use the output from this PLL as the MCGOUT */

Wish it helps you!

If you still have question, please contact me!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------