- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Writing in DDR is inverted

Writing in DDR is inverted

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have a strange problem with DDR.

Project specs:

Kinetis k61FX512

DDR part : MT46V16M16

Using the DDR init script provided in the sample. I have adapted it for DDR and above mentioned part.

I have written a temp function as:

{

volatile uint8_t * u8ptrTmp = (uint8_t *) 0x080000F0;

volatile uint8_t u8Tmp;

volatile uint8_t u8TmpBuff[10];

for(u8Tmp = 0 ; u8Tmp < 10 ; u8Tmp++)

{

u8ptrTmp[u8Tmp] = u8Tmp;

}

for(u8Tmp = 0 ; u8Tmp < 10 ; u8Tmp++)

{

u8TmpBuff[u8Tmp] = u8ptrTmp[u8Tmp];

}

for(;;);

}

Objective is to write 10 bytes starting at 0x08000000 & reading them back in a buffer.

The writing happens but very oddly, like:

0x080000F0 = 0x07

0x080000F1 = 0x06

0x080000F2 = 0x05

0x080000F3 = 0x04

0x080000F4 = 0x03

0x080000F5 = 0x02

0x080000F6 = 0x01

0x080000F7 = 0x00

And reading happens properly as in buffer shows 0x07, 0x06....0x00.

Tried changing endianness, but no luck. It results in

0x080000F0 = 0x04

0x080000F1 = 0x05

0x080000F2 = 0x06

0x080000F3 = 0x07

0x080000F4 = 0x00

0x080000F5 = 0x01

0x080000F6 = 0x02

0x080000F7 = 0x03

DDR config code:

void ext_ddr_init(void)

{

/* Enable DDR controller clock */

SIM_SCGC3 |= SIM_SCGC3_DDR_MASK;

/* Enable DDR pads and set slew rate */

//SIM_MCR |= 0xC4; // bits were left out of the manual so there isn't a macro right now

SIM_MCR |= 0x64; // For DDR instead of DDR2

DDR_RCR |= DDR_RCR_RST_MASK; // Force software reset

//* (vuint32 *)(0x400Ae1ac) = 0x01030203;

* (vuint32 *)(0x400Ae1ac) = 0x00000003; // Since ODT is absent in DDR config

//DDR_CR00 = 0x00000400; // DDRCLS = 4 is reserved??

DDR_CR00 = 0x00000000; //For selecting DDR Class

u32Temp = DDR_CR01; //DDR_CR01 is read only. Gives Maxcol = 11, Max row = 0x10 & CS = 2

//DDR_CR02 = 0x02000031; // Init time & refresh count

DDR_CR02 = 0x0F00FFFF;

//DDR_CR03 = 0x02020506;

DDR_CR03 = 0x1F010506; // delay, 1 for ddr

//DDR_CR04 = 0x06090202;

DDR_CR04 = 0xFF3F0707;

//DDR_CR05 = 0x02020302;

DDR_CR05 = 0x1F070F0F;

//DDR_CR06 = 0x02904002;

DDR_CR06 = 0x009040FF;

//DDR_CR07 = 0x01000303;

DDR_CR07 = 0x01010303;

//DDR_CR08 = 0x05030201;

DDR_CR08 = 0x1F1FFF01;

//DDR_CR09 = 0x020000c8;

DDR_CR09 = 0x02000FFF;

DDR_CR10 = 0x03003207;

DDR_CR11 = 0x01000000;

DDR_CR12 = 0x04920031;

DDR_CR13 = 0x00000005;

DDR_CR14 = 0x00C80002;

DDR_CR15 = 0x00000032; // | DDR_CR15_SREF_MASK ;

DDR_CR16 = 0x00000001;

DDR_CR20 = 0x00030300;

DDR_CR21 = 0x00040232;

DDR_CR22 = 0x00000000;

DDR_CR23 = 0x00040302;

DDR_CR25 = 0x0A010201;

//DDR_CR25 = 0x0A020200;

DDR_CR26 = 0x0101FFFF;

DDR_CR27 = 0x01010101;

DDR_CR28 = 0x00000003;

DDR_CR29 = 0x00000000;

DDR_CR30 = 0x00000001;

//DDR_CR34 = 0x02020101;

DDR_CR34 = 0x00000000;

DDR_CR36 = 0x01010201;

DDR_CR37 = 0x00000200;

DDR_CR38 = 0x00200000;

DDR_CR39 = 0x01010020;

DDR_CR40 = 0x00002000;

DDR_CR41 = 0x01010020;

DDR_CR42 = 0x00002000;

DDR_CR43 = 0x01010020;

DDR_CR44 = 0x00000000;

DDR_CR45 = 0x03030303;

DDR_CR46 = 0x02006401;

DDR_CR47 = 0x01020202;

DDR_CR48 = 0x01010064;

DDR_CR49 = 0x00020101;

DDR_CR50 = 0x00000064;

DDR_CR52 = 0x02000602;

DDR_CR53 = 0x03c80000;

DDR_CR54 = 0x03c803c8;

DDR_CR55 = 0x03c803c8;

DDR_CR56 = 0x020303c8;

DDR_CR57 = 0x01010002;

asm("NOP");

DDR_CR00 |= 0x00000001;

while ((DDR_CR30 & 0x400) != 0x400);

MCM_CR |= MCM_CR_DDRSIZE(0);

}

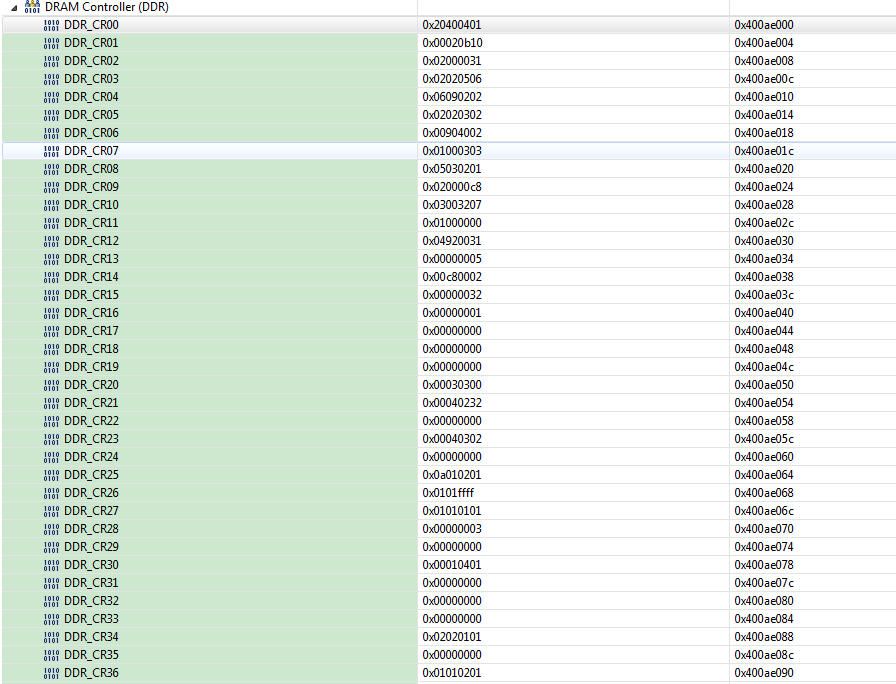

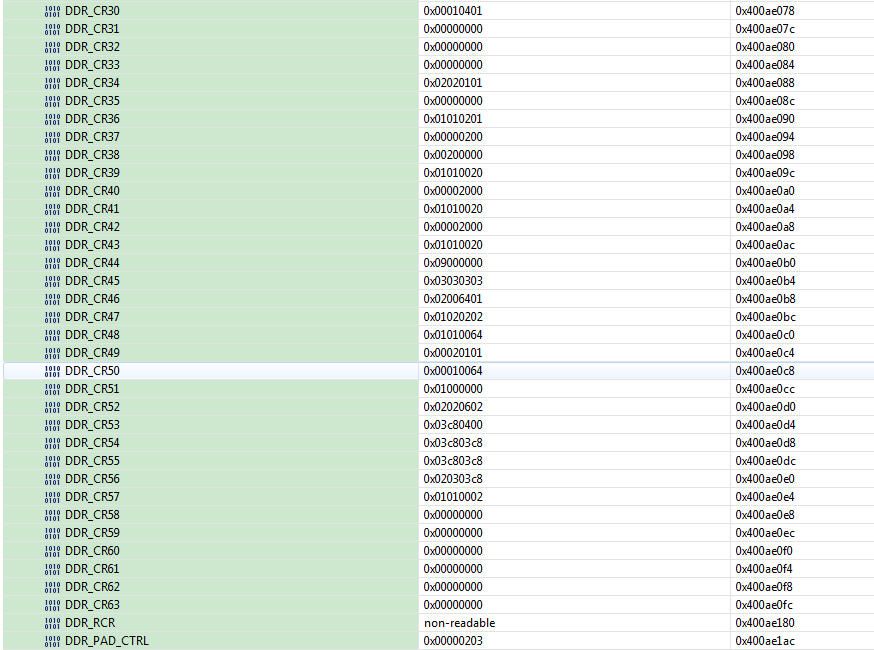

Attached are images of the same

I need to transfer & run code from DDR at bootup. So I need to be able to write & read sequentially byte by byte.

Kindly suggest if anymore details are required.

Thanks...

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the patience.

Please download K70 DDR memory initialization tool from below link, which provide DDR1 memory example about related register setting.

Wish it helps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Besides of hardware connection issue, I think most caused by DDR controller registers setting.

Please check below pictures about TWR-K70F120M board DDR2 registers setting.

Wish it helps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, thanx for replying.

Already tried with the tower config and all sorts of register combinations (well most of them), but no luck

Can you send across or point to some code or sample of K60/K61/K70 interfaced with DDR1 RAM and not DDR2.

Or does freescale have any evaluation board containing Kinetis and DDR 1 RAM??

Thank You

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the patience.

Please download K70 DDR memory initialization tool from below link, which provide DDR1 memory example about related register setting.

Wish it helps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Awesome !!

Working now. Used the tool. Thanks a lot !!