- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- We implemented A/D reading but had issues with the resulting readings

We implemented A/D reading but had issues with the resulting readings

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Mark,

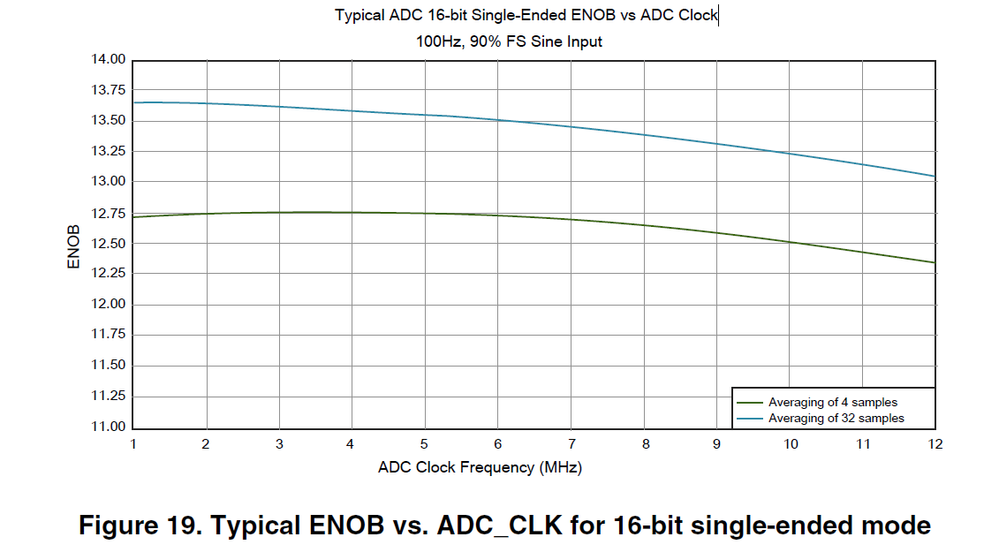

Pls refer to the section 3.6.1.2 16-bit ADC electrical characteristics in data sheet of K65, the fADCK frequency ranges from 1.0MHz to 24MHz for the mode less than or equal to 13 bits mode, or ranges from 2.0MHz to 12Mhz for 16 bits mode.

Regarding the optimum fADCK, we have provided the curve of Typical ADC 16-bit Single-Ended ENOB vs ADC Clock, from the curve, you can see that the ADC16 can give optimum accuacy when the fADCK ranges from 2~6MHz.

I copy the curvbe here:

Hope it can help you

BR

Xiangjun rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Mark,

Pls refer to the section 3.6.1.2 16-bit ADC electrical characteristics in data sheet of K65, the fADCK frequency ranges from 1.0MHz to 24MHz for the mode less than or equal to 13 bits mode, or ranges from 2.0MHz to 12Mhz for 16 bits mode.

Regarding the optimum fADCK, we have provided the curve of Typical ADC 16-bit Single-Ended ENOB vs ADC Clock, from the curve, you can see that the ADC16 can give optimum accuacy when the fADCK ranges from 2~6MHz.

I copy the curvbe here:

Hope it can help you

BR

Xiangjun rong