- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: The UART of the KM34

The UART of the KM34

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

The UART of the KM34

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can the UART of KM34 work in the DMA mode? If yes, is there any example?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

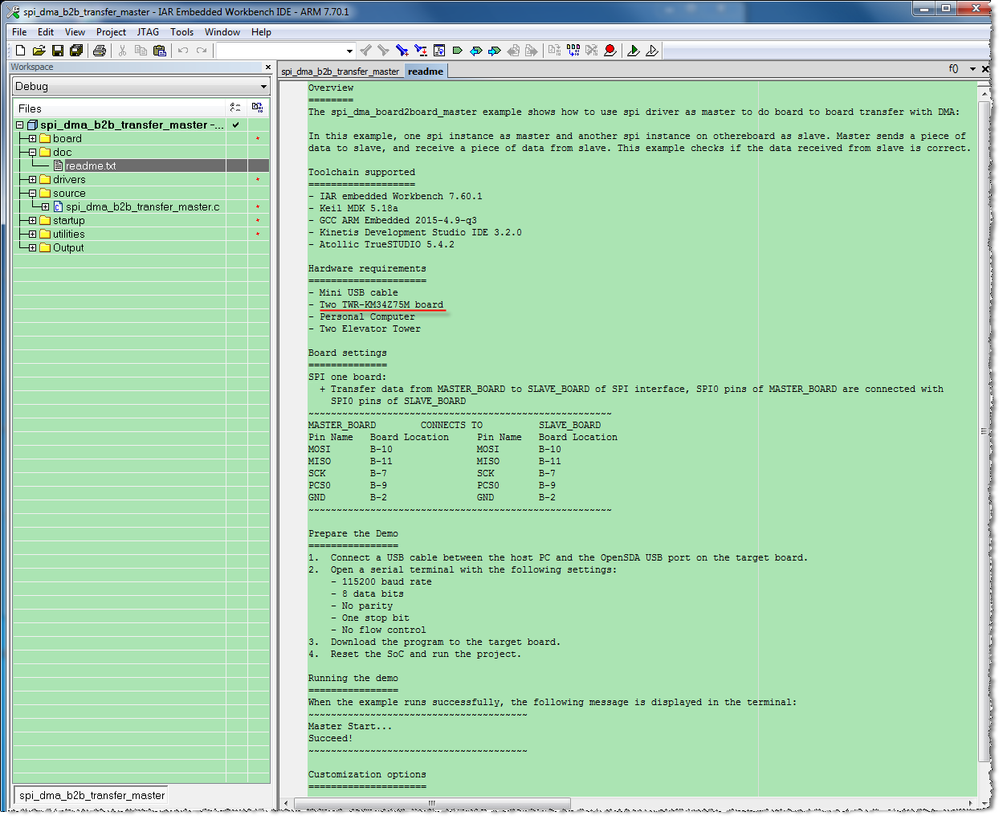

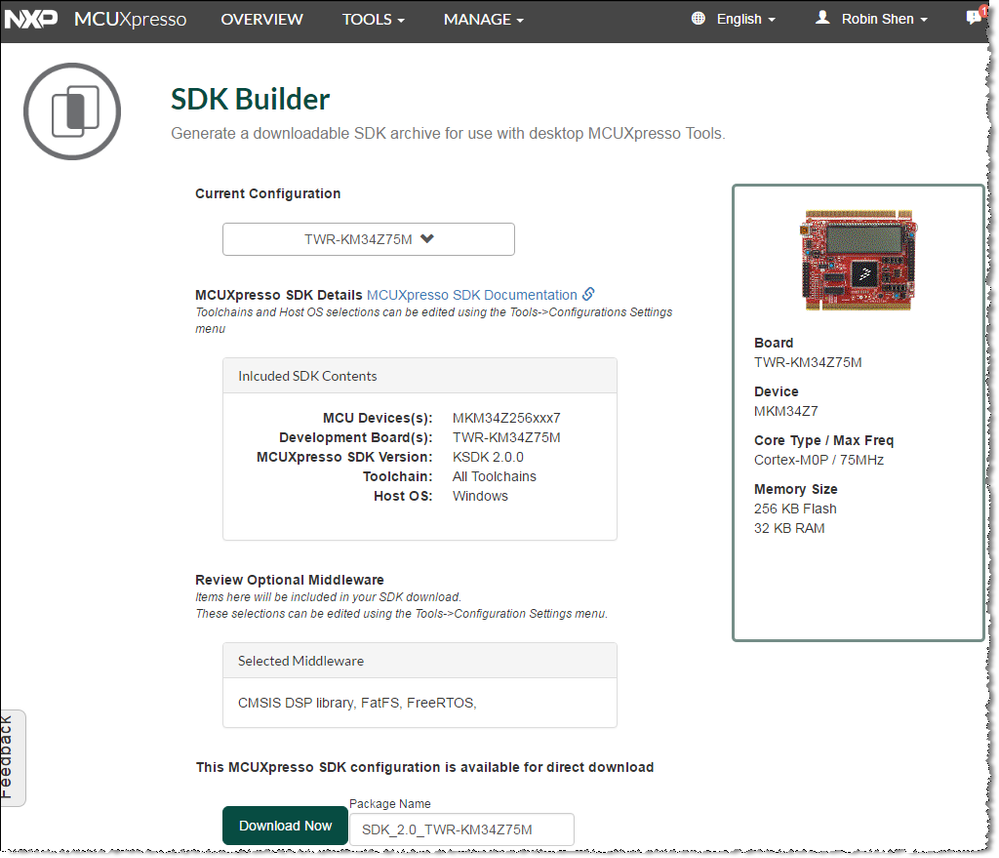

I have used the example "C:\Freescale\SDK_2.0_TWR-KM34Z75M\boards\twrkm34z75m\driver_examples\spi\dma_b2b_transfer\master\iar\spi_dma_b2b_transfer_master.eww" .But the communication result is not successful.What is the reason?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Would you please tell us what kind of error you have meet?

I have only one TWR-KM34Z75M, so I don't have another spi instance on othereboard as slave.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you for your help.The error happens because I have not connected the slave.

Now I have another question.

I transplant the DMA source code to my old project.

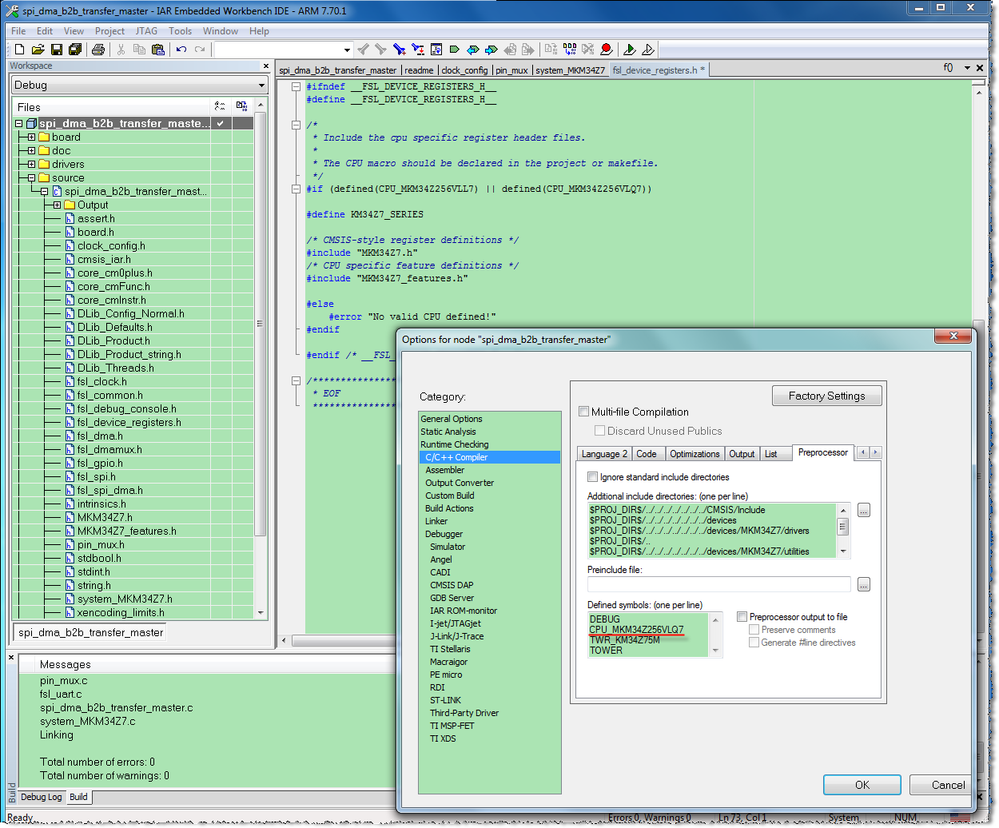

There is an error "No valid CPU defined!" in the file fsl_device_registers.h after the compiling in the my old IAR project.

It happens because I have not define the CPU_MKM34Z256VLL7 and CPU_MKM34Z256VLQ7.

I cannot find where to define CPU_MKM34Z256VLL7 and CPU_MKM34Z256VLQ7 in the example.

Can you tell me where to define the CPU_MKM34Z256VLL7 and CPU_MKM34Z256VLQ7?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You can find it in the Defined symbols:

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you very much.

Now I have another question.

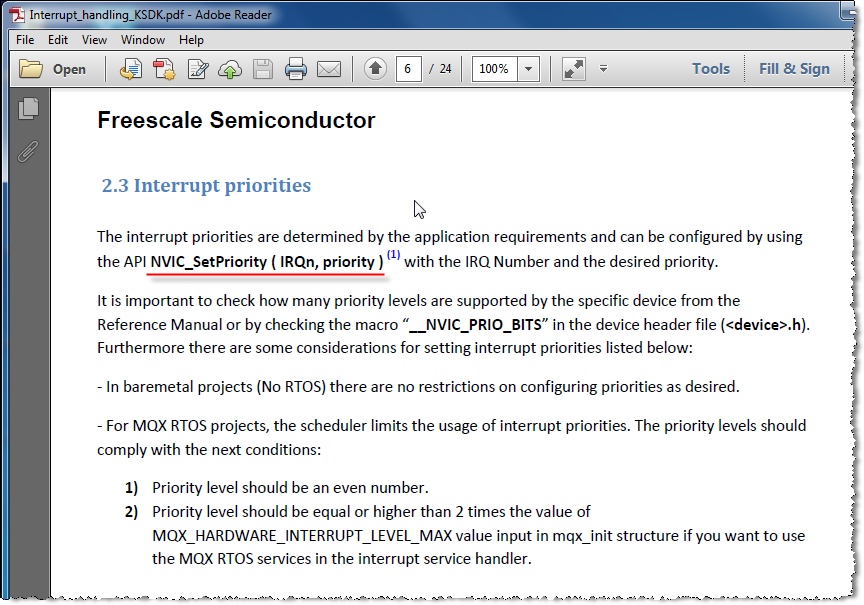

How to set the priority level of the “DMA channel transfer complete interrupt”? I cannot find it in the example.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please use the API NVIC_SetPriority ( IRQn, priority ).

"Interrupt_handling_KSDK.pdf" can be download from Interrupt handling with KSDK and Kinetis Design Studio.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thank you very much.

Now I have another question.

I let the DMA stay in the receiving mode to receive the data from the master.

The steps to let the bug reappear:

1.Start the receiving:

{

uint8_t rx0_buf[10],

uart_transfer_t receiveXfer;

receiveXfer.data = &rx0_buf[0];

receiveXfer.dataSize = 10;

UART_TransferReceiveDMA(DEMO_UART, &g_uartDmaHandle, &receiveXfer);

}

2.Restart the receiving again after receiving a frame

void UART_UserCallback(UART_Type *base, uart_dma_handle_t *handle, status_t status, void *userData)

{

if (kStatus_UART_RxIdle == status)

{

uint8_t rx0_buf[10],

uart_transfer_t receiveXfer;

receiveXfer.data = &rx0_buf[0];

receiveXfer.dataSize = 10;

UART_TransferReceiveDMA(DEMO_UART, &g_uartDmaHandle, &receiveXfer);

}

}

3.If sending 10 bytes in the master 10 times in 1s period, the receiving is OK every time.

Remark: The frame in the master---AA AA AA 8C 01 80 FB 02 00 01

4.But if sending 20 bytes in the master 10 times in 1s period, there is an error for the receiving. The DMA interrupt does not happen anymore after sending 10 times in the master. It seems that the DMA communication is dead.

Remark: The frame in the master----AA AA AA 8C 01 80 FB 02 00 01 12 12 12 12 12 12 12 12 12 12

How to restore the DMA communication in such case? Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Yes. The UART of KM34 can work in the DMA mode.

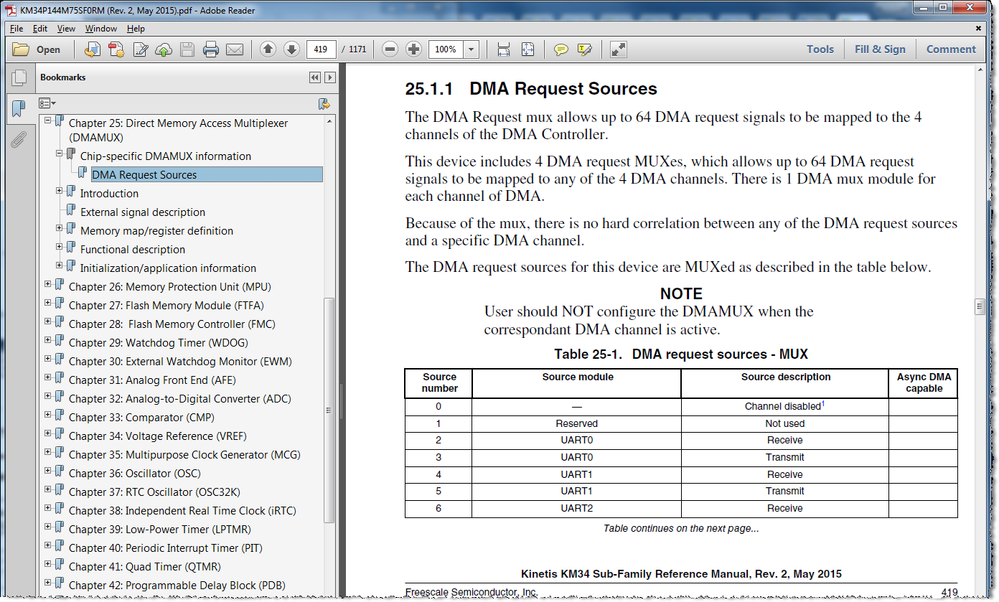

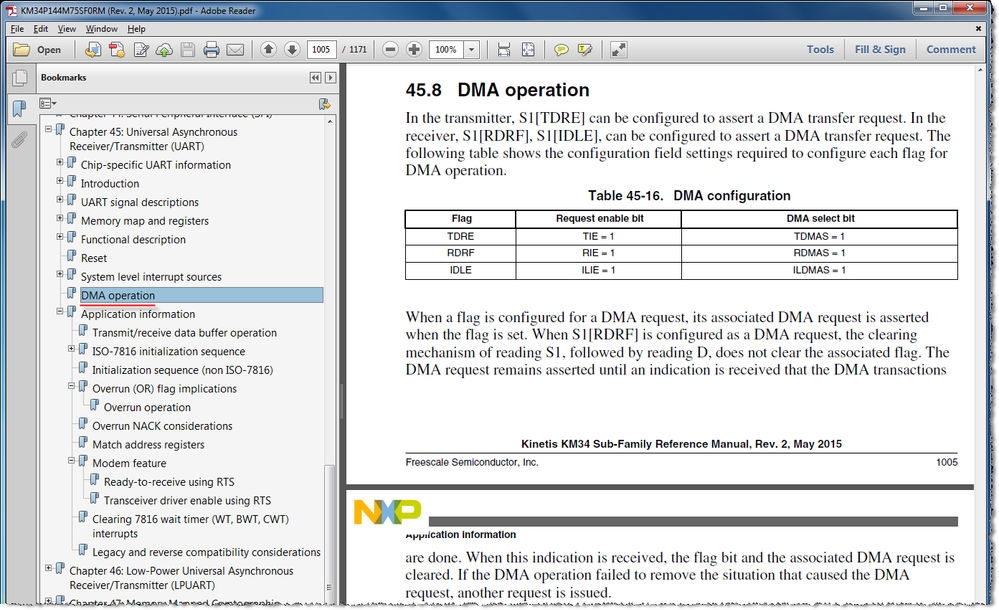

Please check the chapter "25.1.1 DMA Request Sources" and "45.8 DMA operation" in KM34P144M75SF0RM.

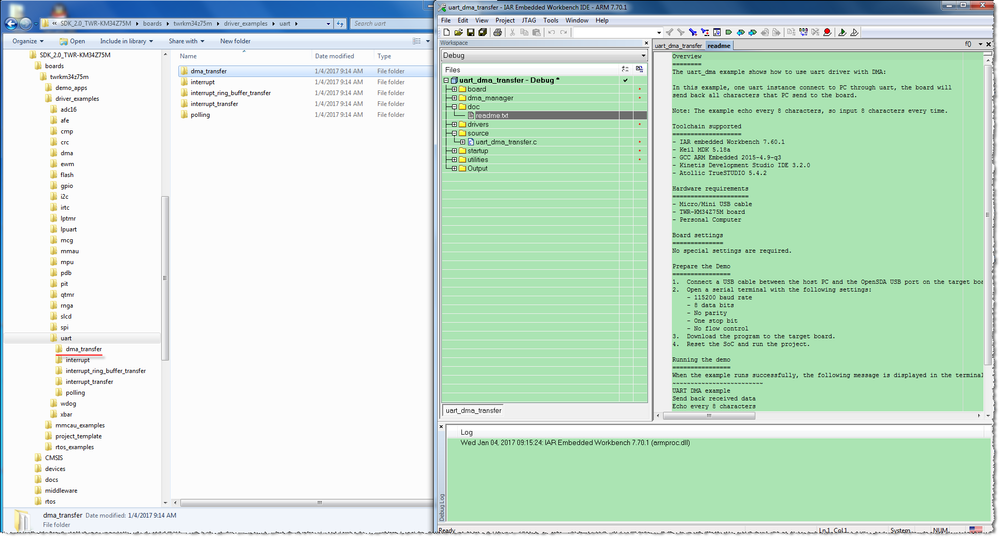

You can refer the example "dma_transfer" in KINETIS-SDK.

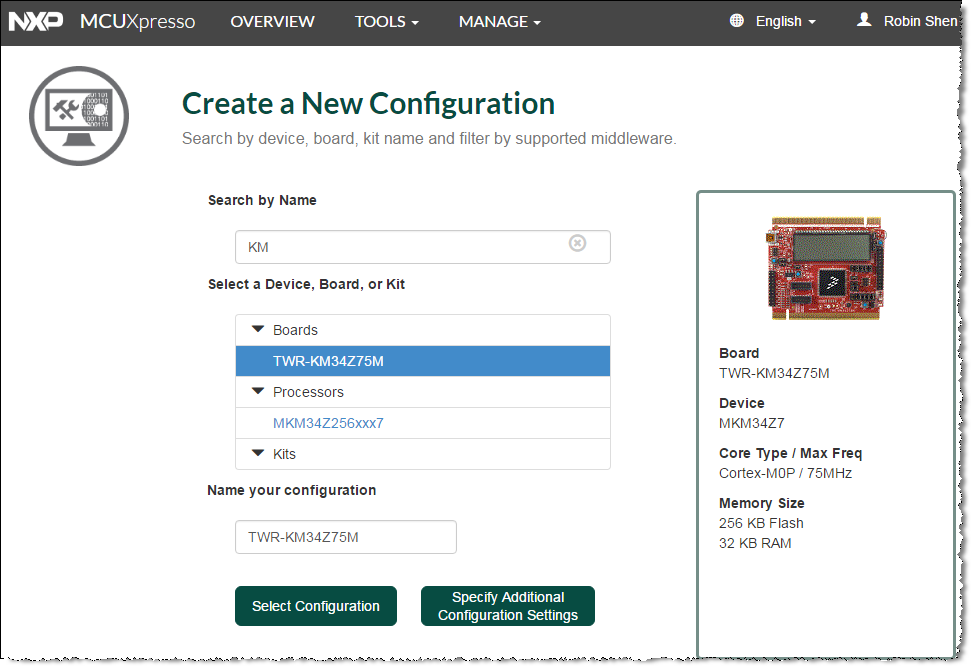

Please search KM34 then select TWR-KM34Z75M and download SDK_2.0_TWR-KM34Z75M.

You can getting start with KSDK reading "How to start with KSDK".

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------