- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: SWOCTRL register seems locked

SWOCTRL register seems locked

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SWOCTRL register seems locked

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MCUXpresso 11.1.1, MKV42F64, barebone, PE Micro Multilink.

I'm trying to set up FTM0 for a straightforward 3-phase drive. Having traversed the minefield of IF statements in the Reference Manual for the synchronization, I still can't update the Software Control (SWOCTRL) register. However, the issue isn't the output, it's trying to change the buffer itself.

I have tried:

FTM0->SWOCTRL = 0x0000yyyyU;

FTM_SetSoftwareCtrlVal(FTM0, 0, true);

FTM_SetSoftwareCtrlEnable(FTM0, 1, true);

Even if I try to do a direct register update while in a breakpoint, the result always comes back all zeros, as if it is a write-only register.

All the other registers update fine, as far as I have explored.

Any suggestions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found a workaround for my application. I was going to use the SW control to drive the enable pin of the driver chip either high (under software) or low (masked). This allows the driver control to be coincident with the PWM with the same write to the OUTMASK register at the moment of motor commutation. However, the same effect can be achieved by simply writing a compare value to the CnV register which exceeds that of the MOD register, which will force it to remain high when unmasked.

This doesn't resolve the original SWOCTRL issue, but I'm spinning a motor!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

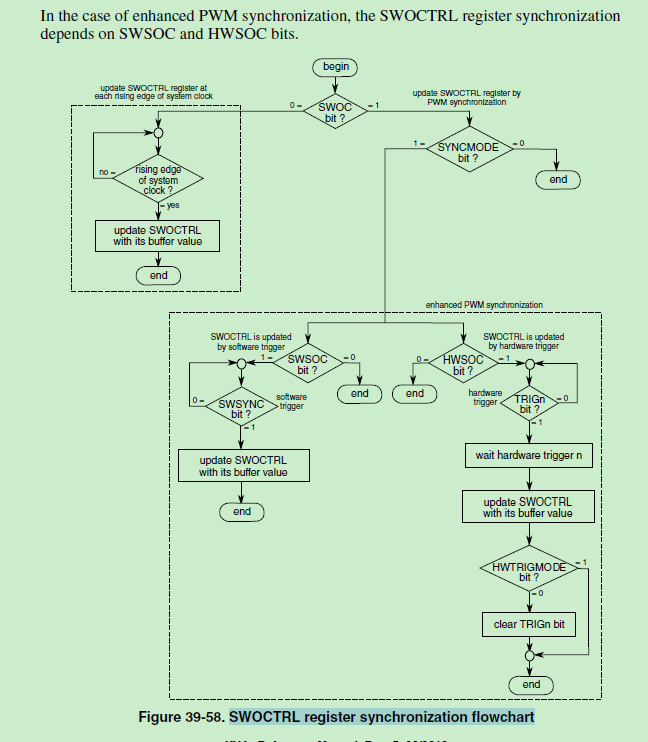

Do you totally follow this flowchart to update the SWOCTLRL?

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I see the issue, now. As I understand, a read/write buffer means exactly that - you can write and then read back the register value. The synchronization step would then be when that register value is passed into the logic itself.

This is not how SWOCTRL (and maybe other registers in the FTM) works. You have to write to the buffer and then perform the synchronization before the value you have just written can be read. If I write the SWSYNC bit in the flow diagram above, after setting SWOC, SYNCMODE & SWSOC and writing to SWOCTRL, the read value in SWOCTRL is correct. The description in 39.4.26 reads "This register has a write buffer. The fields are updated by the SWOCTRL register synchronization." is technically correct, but only after finding out how the register really works! Most people, I think, would read that as the contents written to the register would be buffered until synchronization (which is true and desirable), but not understand that the buffer is before the read register itself. I can see why this could be a desirable functionality, but it needs explaining!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the updated information.

If you read the NXP appliation note: AN4560

https://www.nxp.com/docs/en/application-note/AN4560.pdf

There has the examples, it also update the buffer at first, then do the synchronization

Wish it helps you!

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Malcolm Macdonald ,

How do you check the FTM0->SWOCTRL value?

I check the RM this chapter:

39.5.11 PWM synchronization

The PWM synchronization provides an opportunity to update the MOD, CNTIN, CnV, OUTMASK, INVCTRL and SWOCTRL registers with their buffered value and force the FTM counter to the CNTIN register value.

Note

The legacy PWM synchronization (SYNCMODE = 0) is a subset of the enhanced PWM synchronization (SYNCMODE =

1). Thus, only the enhanced PWM synchronization must be used.

So, do you use the enhanced PWM synchronization?

The SWOCTRL register can be updated at each rising edge of system clock (SWOC = 0)

or by the enhanced PWM synchronization (SWOC = 1 and SYNCMODE = 1) according

to the following flowchart.

Please also check Figure 39-58. SWOCTRL register synchronization flowchart

Do you follow the flowchart?

Wish it helps you!

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply, Kerry.

Yes, I am using SYNCMODE = 1

I am looking for the result principally by looking at the register's value at a breakpoint. The problem isn't the synchronization of the transfer from the buffer contents to the working register (although that is quite confusing in itself, by comparison to, say, the eFlexPWM which I am very familiar with through other projects), but changing the value in the buffer in the first place.