- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- ARM Microcontrollers

- :

- Kinetisマイクロコントローラ・ナレッジ・ベース

- :

- S32K clock mechanism & configuration

S32K clock mechanism & configuration

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

S32K clock mechanism & configuration

S32K clock mechanism & configuration

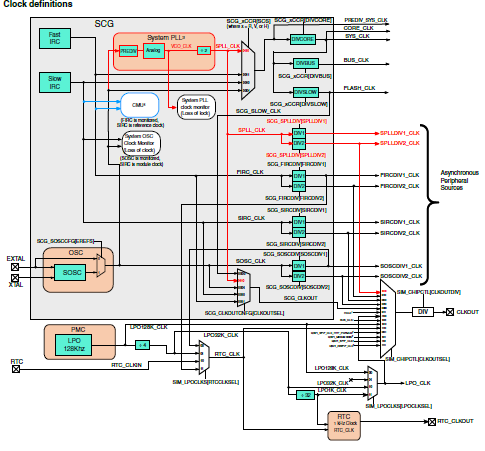

First let us see the clock tree:

Core clock up to 112M, Bus clock up to 56M, Flash clock up to 28M.

Clock can been from: System OSC、Slow IRC 、Fast IRC and System PLL

1. OSC

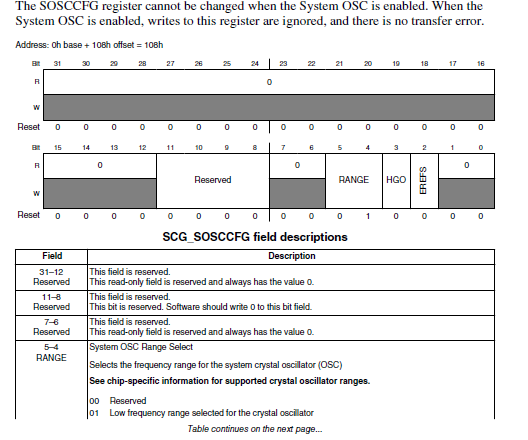

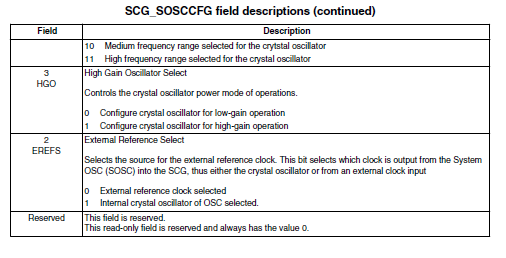

SCG_SOSCCFG

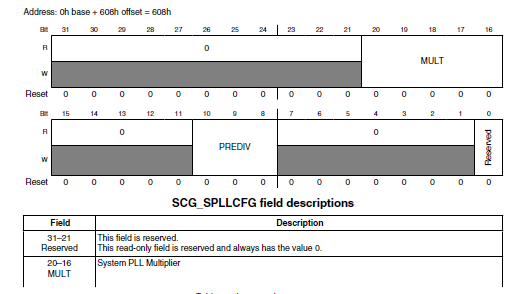

2. PLL configuration

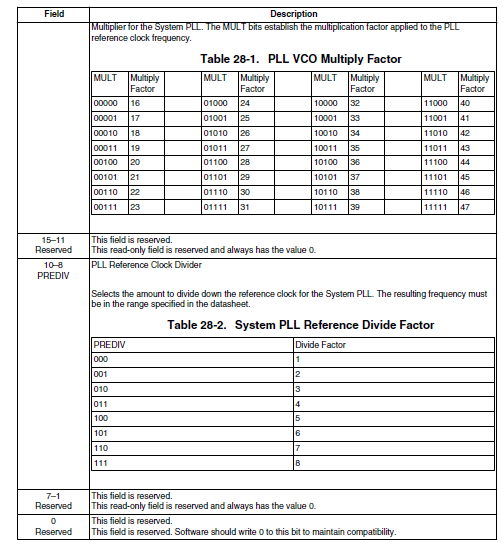

formula: SPLL_CLK = (VCO_CLK)/2

VCO_CLK = SOSC_CLK/(PREDIV + 1) *(MULT + 16)

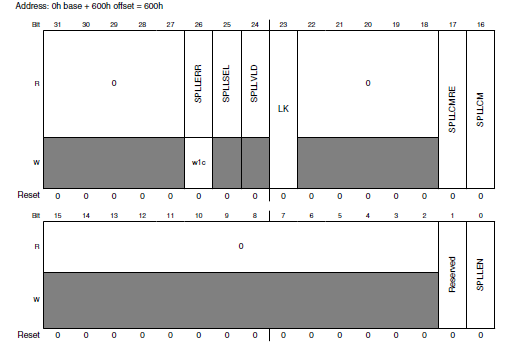

3. SCG_SPLLCSR

void SystemClockInit(void)

{

SCG->SOSCCFG = 0x3C;

SCG->SOSCCSR |= 1<<0; /* SOSCEN=1 enable SOSC clock */

/*wait clock active*/

while((SCG->SOSCCSR & SCG_SOSCCSR_SOSCVLD_MASK) == 0);

SCG->SPLLCSR &= ~(0x1<<0) ; /* SPLLEN=0: disable PLL*/

SCG->SPLLCFG &= ~(0x7<<8); /* PREDIV=0: 1 */

SCG->SPLLCFG |= 0xCU<<16; /* MULT=12: 28 PLL VCO = 8/1*(12+16) = 224M */

SCG->SPLLCSR |= 0x1<<0; /* SPLLEN=1: enable PLL */

/* wait PLL active*/

while((SCG->SPLLCSR & SCG_SPLLCSR_SPLLVLD_MASK) == 0);

SCG->RCCR |= SCG_RCCR_DIVCORE(0); /* DIVCORE=0: 1, CORE/SYS_CLK 112MHz */

SCG->RCCR |= SCG_RCCR_DIVBUS(1); /* DIVBUS=1: 2, BUS_CLK 56MHz */

SCG->RCCR |= SCG_RCCR_DIVSLOW(3); /* DIVSLOW=2: 4 FLASH_CLK is 28MHz */

SCG->RCCR &= 0xFEFFFFFF; /* Initially set to SIRC so that LSB could be set as '0' */

SCG->RCCR |= SCG_RCCR_SCS(6); /* SCS=6: system clock System PLL */

}