- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Please let me know when Lockup event occurs

Please let me know when Lockup event occurs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sirs or Madams,

Could you please let me know when Lockup event occurs?

I now understand that the LockUp event can occur when the frequency of system clock of K61 is set too fast,

thanks to supports of NXP engineers.

But, I want to know whether there are any other factors which can cause LockUp event,

in addition to excessively high frequency of the system clock.

Best regareds,

Shinsuke Tanaka

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Sorry for the late response. Answer to your questions, see below:

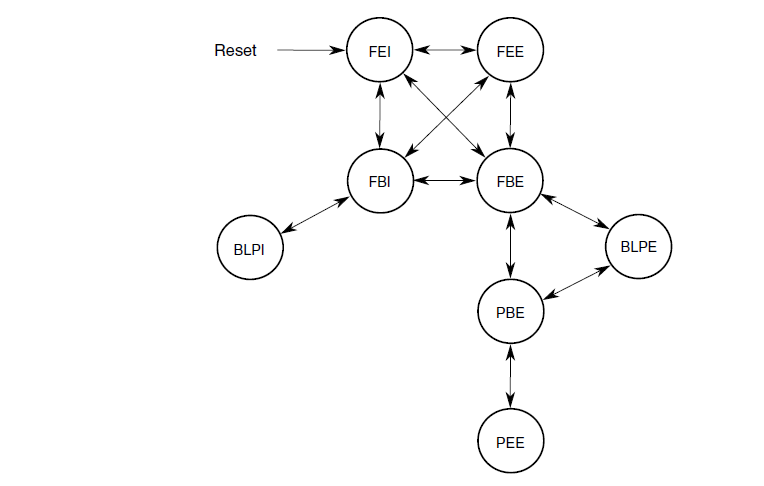

1. The Clock transition not just mean MCG_C1 changing. See below diagram. These are the MCG restricted transitions modes.

2. Yes, your understand is correct.

3. Here means all system memory and memory interface.

4. Yes, this maybe also cause the lockup.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

First please note that the DDR clock duty cycle should be guaranteed by the chip design to be close to 50%, and any violating will led access DDR error, that is different from lockup.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

There really has a few of factors that led to system lockup, from core to bus. Just for examples that may cause core lockup:

1. An incorrect Clock mode transition occurs

2. The clock part is over-clocked

3. Code executes after POR, if a part memory is not programmed

4. Broken external oscillator

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mr.Li,

I appreciate your information.

Could you please respond to my additional questions to your feedbacks shown below?

1. An incorrect Clock mode transition occurs

-> I now guess that "Clock mode transition" means the changes of values stored on the registers

prepared for clock settings, such as MCG_C1 register.

Is my guess correct?

If my guess is correct, please let me know what "incorrect" means in detail.

2. The clock part is over-clocked

->Does this mean that the frequencies of clocks used inside K61 are set to excessively high?

3. Code executes after POR, if a part memory is not programmed

->Does the "memory" mean the DDR connected to K61 externally?

4. Broken external oscillator

->Will LockUp also occur when Circuit Matching between K61 and external crystal oscillator is NOT adjusted appropriately

on the PCB?

I'm sorry to bother you repeatedly, but I need your help to deepen my understandings.

Best regards,

Shinsuke Tanaka

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Sorry for the late response. Answer to your questions, see below:

1. The Clock transition not just mean MCG_C1 changing. See below diagram. These are the MCG restricted transitions modes.

2. Yes, your understand is correct.

3. Here means all system memory and memory interface.

4. Yes, this maybe also cause the lockup.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Fang Li,

I'm sorry for my repeated questions on LockUp.

But, please let me have one more question on it.

Q.

If "High width" percentage and "Low width" percentage of the clock signal outputted from

K61 DDR_CK pin and DDR_CKB pin does is smaller than those required by DDR connected to K61,

is it possible that the smaller High/Low pulse percentages cause LockUp event?

For example, if "High width" percentage and "Low width" percentage of the clock signal are 35%/35%

but DDR connected to K61 requires that the percentages should be bigger than 45%/45%,

is it possible that this situation causes LockUp event?

Best regards,

Shinsuke Tanaka