- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- NXP ICS LOC Reset

NXP ICS LOC Reset

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NXP ICS LOC Reset

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In a project where we use NXP MKE04Z128VQH4, we are having MCU reset problem.

When we check the SIM_SRSID register after reset, the reset cause is seen as ICS loss-of-clock (LOC). However ICS_C4[CME] is not set.

Can you help with the cause and solution of the problem?

Information about the design can be found below and in the attachment.

MCU | : | MKE04Z128VQH4 |

XTAL | : | AWSCR-8.00MES-C15-T |

OSC_CR | : | 0b10110101 |

ICS_C1 | : | 0b00011010 |

ICS_C2 | : | 0b00100000 |

ICS_C3 | : | 93 |

ICS_C4 | : | 0b00000000 |

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I see that you connect 8MHz crystal to the XTAL/EXTAL pins for KE04.

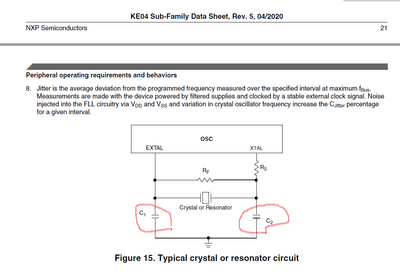

1)I have checked your crystal connection, you do not connect the capacitors as the following Fig.

2)You set the OSC_CR[RANGE]=1, OSC_CR[HGO]=0, so you use high frequency,low power mode.

Pls try to set both the RANGE and HGO bits and have a try.

21.6.2.3 High-frequency, high-gain mode

In high-frequency, high-gain Mode (OSC_CR[RANGE] = 1, OSC_CR[HGO] = 1), the

oscillator uses a simple inverter-style amplifier. The gain is set to achieve rail-to-rail

oscillation amplitudes.

The oscillator input buffer in this mode is single-ended. It provides low pass frequency

filtering as well as hysteresis for voltage filtering and converts the output to logic levels.

21.6.2.4 High-frequency, low-power mode

In high-frequency, low-power mode (OSC_CR[RANGE] = 1, OSC_CR[HGO] = 0) the

oscillator uses a gain control loop to minimize power consumption. As the oscillation

amplitude increases, the amplifier current is reduced. This continues until a desired

amplitude is achieved at steady-state.

The oscillator input buffer in this mode is differential. It provides low pass frequency

filtering as well as hysteresis for voltage filtering and converts the output to logic levels

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

MCU was waking up and going back to sleep every 25 seconds, so we reduced this to 2 seconds to replicate the error. At the end of the test, we saw that the processor entered a hard fault. We added while into the hard fault function and debugged it with Attach to Running Target.

After turning off the timer clock(SIM->SCGC &= ~0x2u), we saw that ISR_pit_ch1 (timer interrupt)(PIT->CHANNEL[1].TFLG |= 0x1u) came and this caused the error. Do you think LOC reset could be related to this problem?

Thank you for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I do not think that hardfault error can necessarily lead to reset.

BR

XiangJun Rong