- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- MKV46 Interrupt Delay

MKV46 Interrupt Delay

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MKV46 Interrupt Delay

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello NXP Community,

i'd like to ask you about a Problem i have encountered in one of my Projects.

I have set up a SPI Communication on a KV46 running at full Clock Speed. All the Bus Clocks are set to their maximum possible Speed, too. I use the CS-Signal of the SPI via a Port-Interrupt (rising Edge) to detect the End of the SPI Message, because this simplifies the whole operation a lot.

The strange thing is that there is a pretty big time delay of around 1µs between the rising edge of the CS Signal at the Pin and the moment the MCU enters the interrupt Routine.

I have checked if there are any Filters enabled on this Portpin and if the Port really is clocked at it's full speed.

I also tried to look up the maximum values for this kind of time delay, but wasn't able to find any information in the documentation provided by NXP.

I'd like to minimize this Delay, Does anybody have an Idea how i can get rid of it?

Thanks a lot!

Best Regards,

Tobias

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I get you.Before entering the ISR,the controller need to push some data likes PC and some temp data.You can debug and find how many command need to run(assembly) and if possible you can reduce some data or function ,it will get rid of it.

Jianyu:

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

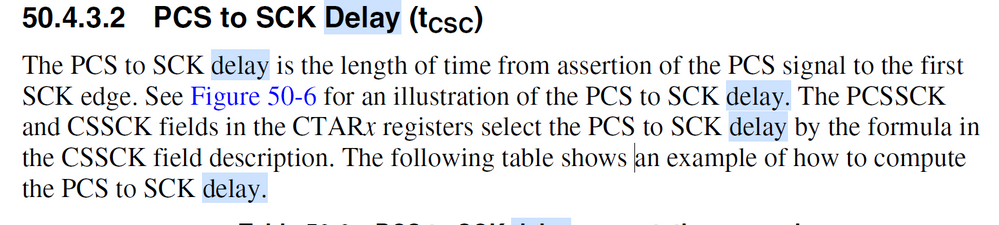

According to the picture above,there has a programmable delay between assertion of the PCS signal to the first SCK edge.

It seems this cause a 1us delay.

The delay can be set from register CTAR when as a master or CTAR0 when slave.

More details get from reference manual.

Jianyu:

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jianyu Chen,

thaks a lot for your reply.

If i get you right, you are referring top the SPI peripheral internal delays. As far as i understand those delays, they don't come to effect in this particular case.

Although i use the Pin assigned to the PCS-Signal of the SPI, which happens to be PC5, i don't use the SPI-Internal interrupts.

I chose to use the Port-Based interrupt (PORTC_PCRN5 field IRQC = 1001), so when the SPI frame is done, PCS goes high which triggers the external Port Interrupt.

What i observe is a 1µs time delay between PCS going high and the controller entering the ISR.

Best Regards,

Tobias