- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- MKV10Z64 - VLPS - high current draw

MKV10Z64 - VLPS - high current draw

MKV10Z64 - VLPS - high current draw

Greetings. I am using the above MCU in a device I am developing. Sleep current in VLPS is ~380uA (confirmed that this is the draw of the MCU alone). Per the datasheet, it should be much much lower. I am using the functions per SDK2.2 to enter VLPS, I am seeing a drop from run time draw (~2mA) to this sleep current draw, so I know that the MCU is entering a lower power state, but I cannot achieve the numbers I expect. All un-used pins are pulled low using internal pull downs and driven low (excluding the JTAG lines - although I suppose I could add them to the list too). Any ideas about what else I should check? Is something defaulted to on (via SDK2.2 or otherwise) that I should be disabling? I believe the core clock is disabled in VLPS so no value in dropping clock speed when sleeping, correct?

Any help is appreciated!

-Chris

Test the same project and same MCU with two FRDM-KV10Z boards, get different current in VLPS.

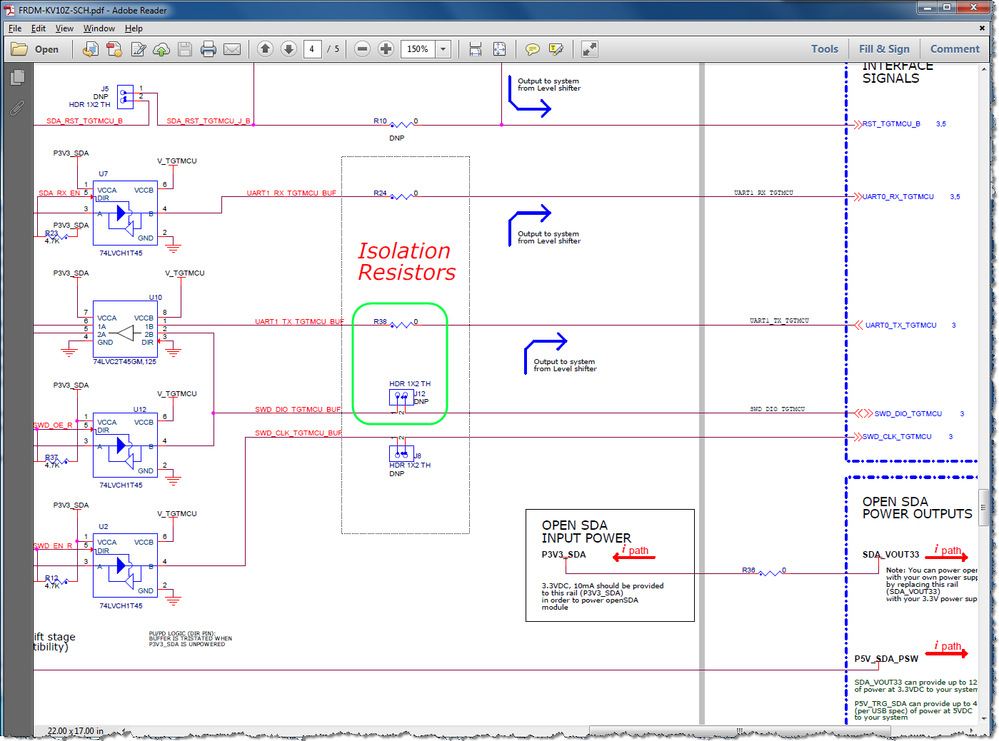

Compare hardware of the FRDM-KV10Z, find the J12 will lead the current leakage. After cut the trace of J12 at bottom side, the current in VLPS of my FRDM-KV10Z board down to about 40μA.

Test the same project and same MCU with two FRDM-KV10Z boards but using different firmware applications for onboard OpenSDA, get different current in VLPS.

Compare firmware application of onboard OpenSDA, find different J-Link firmware will set different voltage to UART1_TX_TGTMCU_R. When use newest Board-Specific Firmwares'19_OpenSDA_FRDM-KV10Z.bin', the PTB17/UART0_TX current leakage occurs.

Conclusion:

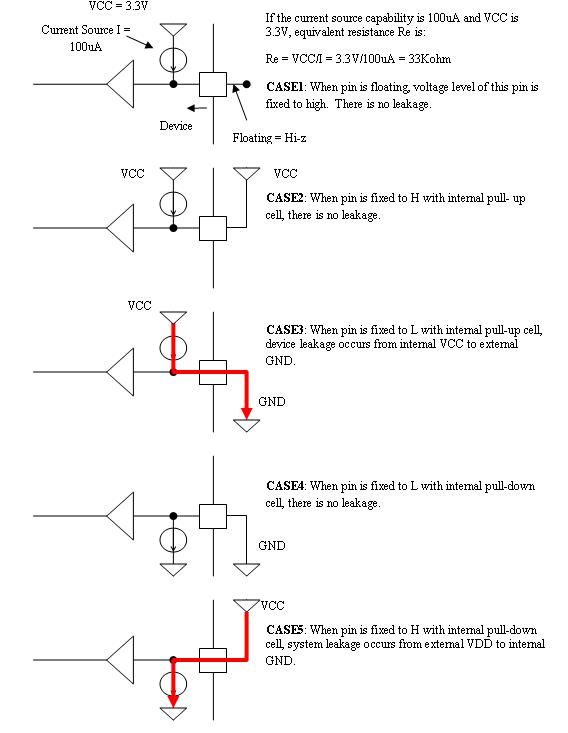

We think it meet the 'Internal pull-up/down case' in Optimizing IO Power Consumption. Customer should avoid this.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------