- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: LDOK bit is not setting in Status and Control register (PDBx_SC)

LDOK bit is not setting in Status and Control register (PDBx_SC)

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LDOK bit is not setting in Status and Control register (PDBx_SC)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP,

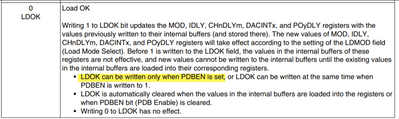

I am not able to set the LDOK Bit in the Status and Control Register (PDBx_SC) for only some particular configurations of the PDBx_SC Register. The configuration is mentioned below:

| TRGSEL | LDMOD | PRESCALER | MULT | CONT | PDBx_SC Reg(expected) | PDBx_SC Reg(actual) |

| 0x0 | 0x0 | 0x0 | 0x0 | false | 0x81 | 0x80 |

| 0x4 | 0x0 | 0x4 | 0x0 | false | 0x4481 | 0x4480 |

| 0x8 | 0x0 | 0x0 | 0x0 | false | 0x881 | 0x880 |

| 0xC | 0x0 | 0x4 | 0x0 | false | 0x4C81 | 0x4C80 |

For the above values in SC Register only, the LDOK is not setting.

Please let me know your inputs on the above issue.

Thanks in advance.

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Parth,

Could you please confirm if you are enabling PDBEN before trying to set LDOK? If so, please share the code you are using to test this so I can replicate it on my side. If you are configuring both bits at the same time please try to set PDBEN first just to be sure.

Best regards,

Felipe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Felipe,

Thanks for your response.

Yes, I am setting the PDBEN before setting the LDOK bit in SC Register. As I mentioned in the parent ticket that only for some configurations I am not able to set the LDOK bit. Apart from those configurations, the LDOK bit is getting set.

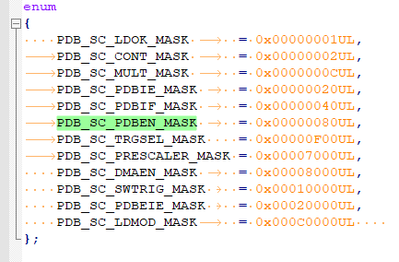

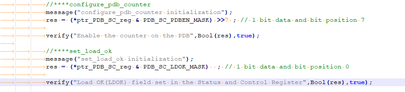

The snip of the test code (not development code) is attached below, where PDBEN is getting set first then the LDOK Bit and in the test results also, for all configurations, the PDBEN is getting set and getting the return value as "True".

Mask Values :

If possible can we connect over a call?

Please provide your inputs.

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Parth,

I did a quick test using KE16Z (I am working to get KE18F) using same register values as you and found something interesting.

I also was not able to see that LDOK bit was set, however, I think this is because the module automatically clears this bit when the values in the internal buffers are loaded.

As you can see in the video attached, LDOK bit does not seem to be set, however, MOD and IDLY registers are correctly updated. Do you see same behavior on your side?

Best regards,

Felipe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for your reply.

Yes, I saw the same behavior, and MOD and IDLY registers are correctly updated on writing '1' to LDOK field but not able to see the '1' written on LDOK bit as the processor clears the LDOK automatically after updating the MOD and IDLY and this is happening very quickly.

But I am able to verify the LDOK is setting to 1 but for below 4 configuration of SC Register only I am not able to verify/set LDOK to '1':

{ TRGSEL, LDMOD ,PRESCALER, MULT , CONT , res_pdb_sc_reg_val }

{ 0x0, 0x0 , 0x0 , PDBDriver::MULT_ONE , false , 0x81 },

{ 0x4, 0x0 , 0x4 , PDBDriver::MULT_ONE , false , 0x4481 },

{ 0x8, 0x0 , 0x0 , PDBDriver::MULT_ONE , false , 0x881 },

{ 0xC, 0x0 , 0x4 , PDBDriver::MULT_ONE , false , 0x4C81 },

For other configurations I am able set/verify for the LDOK, for eg:

{ 0x1 , 0x1 , 0x1 , PDBDriver::MULT_TEN , true , 0x41187}

{0x2 , 0x2 , 0x2 , PDBDriver::MULT_TWENTY, false , 0x82289}

etc...

Only when the MULT bit is set to "MULT_ONE" and CONT bit is "false" then only I am facing this issue.

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Parth,

MULT_ONE is the multiplication factor of the prescaler divider for the counter clock. This means that if the multiplication factor is bigger, the PDB clock will be slower.

In my opinion it makes sense that when PDB clock is faster you are not able to read the LDOK bit as the controller already cleared it when you read it. On the other hand, if PDB clock is slower what I think is happening is that the controller has not yet loaded MOD and IDLY registers when you read LDOK bit in a different instruction.

Best regards,

Felipe

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告